Данная статья является частью научно-исследовательской работы и магистерской диссертации, выполненной по плану обучения в магистратуре СПБГЭТУ «ЛЭТИ» и программы «Два диплома» между СПБГЭТУ «ЛЭТИ» и ТУ Ильменау (Германия) в рамках дисциплины «Междисциплинарный курсовой проект». Данная статья написана в ходе прохождения практики в ТУ Ильменау, в ходе которой были проведены моделирования свойств n-канальных MOSFET транзисторов с параметрами, соответствующими данным международной дорожной карты технологии полупроводников. Моделирования и симуляции проводились в программном пакете ATLAS.

Ключевые слова: МДП-транзистор, MOSFET, индуцированный канал, ATLAS, моделирование

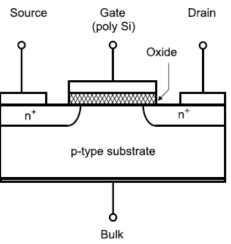

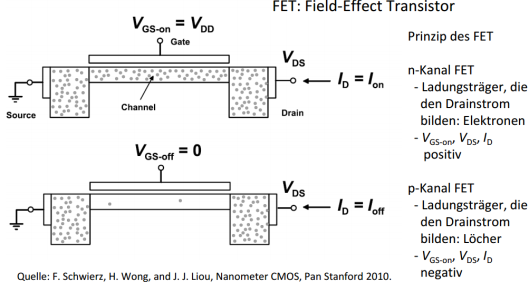

Цель работы — создание структур (n-канальных MOSFET транзисторов) с топологическими нормами, представленными в дорожной карте развития полупроводниковых технологий, с последующим моделированием их свойств и определением требуемых параметров (Vt_lin, Vt_sat, Ion, Ioff). МДП-транзистор (англ. MOSFET) — разновидность полевого транзистора с изолированным затвором, где затвор отделён от активного слоя слоем диэлектрика (обычно диоксид кремния). Это позволяет избавиться от таких недостатков полевых транзисторов, как захват и рассеивание носителей заряда на границе активного слоя. Управление МДП-транзистором осуществляется с помощью напряжения на затворе. Так, для MOSFET с индуцированным n-каналом, приложение положительного напряжения на затворе обедняет p-область активного слоя основными носителями, и при превышении порогового значения напряжения создаёт слой с инверсионным слоем проводимости (n), который соединит области стока и истока n-каналом, по которому и потечет ток. Полевые транзисторы являются основой современной электроники и применяются в различных устройствах, например таких как сенсоры (подробно описывается в [1]).

Рис.1. Типовая структура МДП-транзистора с индуцированным n-каналом [2]

Рис. 2. Принцип работы полевого транзистора [2]

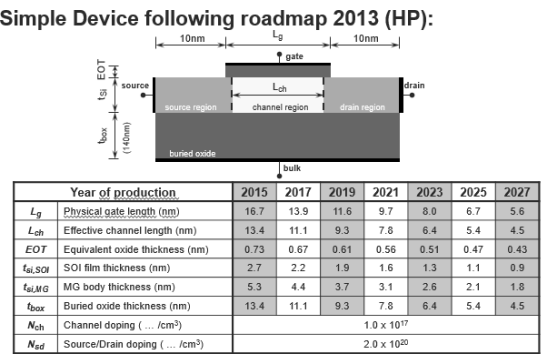

Рис. 3. Данные дорожной карты:Lg — физическая длина затвора; Lch — эффективная длина канала; EOT — эквивалентная толщина оксида; tsi,SOI — толщина активного слоя кремния (1-ый вариант); tsi,MG — толщина активного слоя кремния (2-ой вариант); tbox — толщина погребенного оксида (140 нм или вариация); Nch — уровень легирования канала; Nsd — уровень легирования истока и стока

В качестве отправных точек были взяты параметры для 2015, 2019, 2023, 2027 годов. По данным дорожной карты было построено 16 структур (четыре типа структур по годам (с индивидуальными значениями толщины оксидной плёнки, длины затвора и канала), для каждой из этих структур ещё по две с вариацией толщины активного слоя, и ещё по две с изменением толщины нижнего слоя оксида).

Построение структур осуществлялось в программном пакете ATLAS.

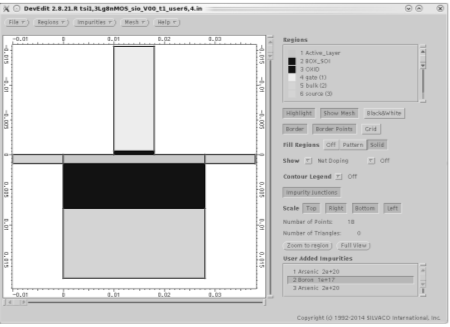

Рис. 4. Типовая структура MOSFET транзистора

Для построенных структур создавалась сетка, в узлах которой программа рассчитывала все необходимые параметры. После задания сетки задавались необходимые параметры транзистора (рабочее напряжение, максимальная скорость носителей заряда для модели, которая использовалась при симуляциях (использовалась CVT модель), и т. д.). Затем программа проводила расчеты, и для каждой структуры были получены значения необходимых параметров, а также вид стокозатворных характеристик. Надо отметить, что для более наглядного сравнения исходные параметры транзистора, а именно работа выхода материала затвора, подбирались таким образом, чтобы значение тока Ioff было равно 0.1 μA.

Полученные результаты:

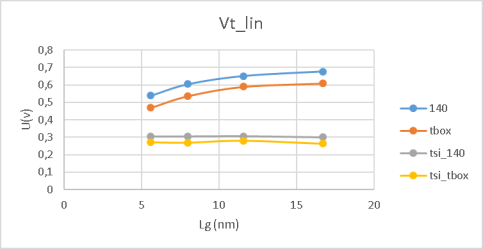

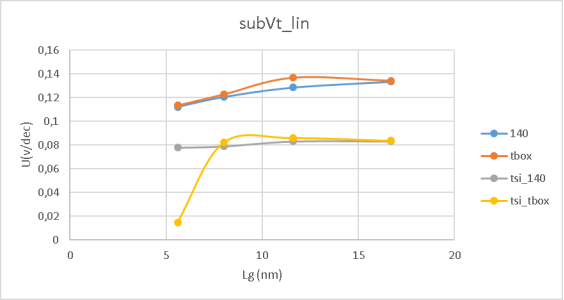

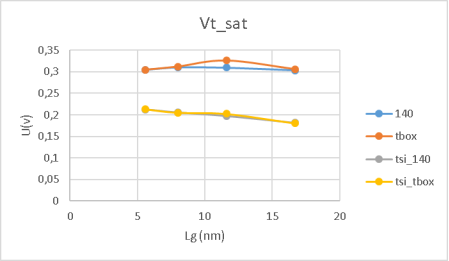

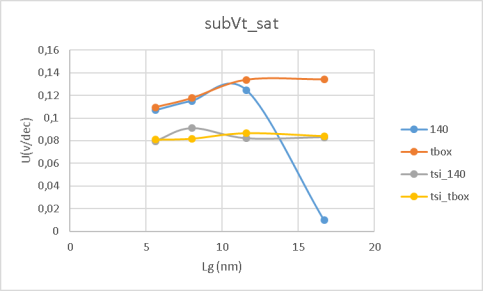

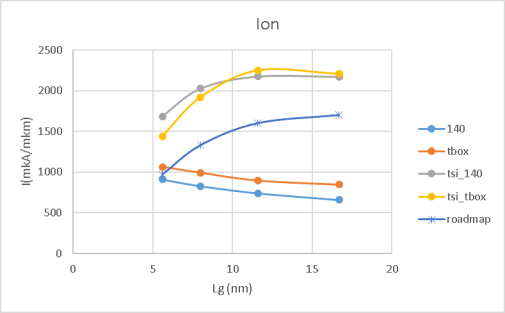

Результаты для всех структур были разбиты на 4 группы: 1) структуры с более толстым активным слоем (tsi= tMG) и толстым погребенным оксидом (tbox= 140 нм). 2) структуры с более толстым активным слоем (tsi= tMG) и тонким погребенным оксидом (tbox= tbox из дорожной карты). 3) структуры с более тонким активным слоем (tsi= tSOI) и толстым погребенным оксидом (tbox= 140 нм). 4) структуры с более тонким активным слоем (tsi= tSOI) и тонким погребенным оксидом (tbox= tbox из дорожной карты).

Для каждой группы структур созданной программой были рассчитаны следующие параметры: Vt_lin (значение напряжения при пороговом значении тока (setIth= 2.00e-07 / ($Lgate*1.0e-03)) при рабочем напряжении (напряжение сток-исток) равном 50 mV), Vt_sat(значение напряжения при пороговом значении тока (setIth= 2.00e-07 / ($Lgate*1.0e-03)) при рабочем напряжении (напряжение сток-исток), равном значению из дорожной карты для данного года (0,83, 0,77, 0,71 или 0,65 В), subVt_lin, subVt_sat(параметры, характеризующие качество кривизны характеристик (расчёт представлен в демонстрационной программе)), а также Ioff и Ion (значения токов при напряжении затвор-исток равном 0 и при напряжении затвор-исток, равном рабочему напряжению соответственно).

Рис. 5. Зависимость Vt_lin от длины затвора при Ioff= 0,1 μA

Рис. 6. Зависимость subVt_lin от длины затвора при Ioff= 0,1 μA

Рис. 7. Зависимость Vt_sat от длины затвора при Ioff= 0,1 μA

Рис. 8. Зависимость subVt_sat от длины затвора при Ioff= 0,1 μA

Рис. 9. Зависимость Ion от длины затвора при Ioff= 0,1 μA

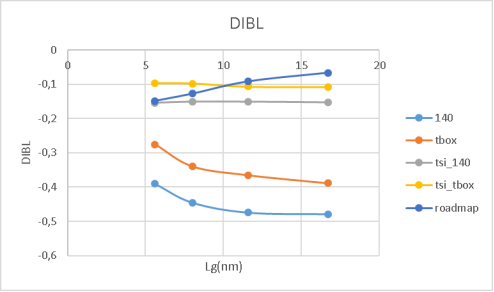

Ещё один параметр качества транзистора — DIBL (DrainInducedBarrierLowering). DIBL характеризует идеальность семейства кривых тока стока от напряжения затвор-исток. Чем ближе значение DIBL, тем «идеальней» транзистор.

Рис. 10. DIBL смоделированных структур и дорожной карты

Анализ результатов: Полученные данные говорят о том, что только транзисторы с более тонким активным слоем удовлетворяют требуемым параметрам дорожной карты, прежде всего это касается значений параметров DIBL и Ion. Использование толстого активного слоя позволяет приблизиться к необходимым значением параметров транзистора, но только при малых значениях ширины затвора. Поэтому можно сделать вывод о неэффективности потенциального применения транзисторов с толстым активным слоем.

Заключение: Проведенные симуляции позволяют спрогнозировать свойства транзисторов с параметрами и топологическими нормами, которыми должны будут обладать транзисторы в рамках дорожной карты, которая, в свою очередь, базируется на правиле Мура — основном законом развития современной электроники. Такое моделирование поможет оптимизировать и усовершенствовать работу транзисторов в будущем, а также подсказать правильное направление в выборе материалов и параметров структуры электронных устройств.

Данная работа является подготовительным шагом к написанию магистерской диссертации, в которой будут рассматриваться JunctionlessMOSFET, управление свойств которых будет осуществляться с помощью изменения уровня легирования в активном слое кремния.

Литература:

1 Зятьков И. И., Максимов А. И., Мошников В. А. Сенсоры на основе полевых транзисторов DJVU. Санкт-Петербург, издательство СПбГЭТУ «ЛЭТИ», 2002. — 56 с. Учебное пособие

2 F. Schwierz, H. Wong, J. J. Liou, „Nanometer CMOS“, Pan Stanford, Singapore 2010