В сравнении с традиционным двумерным MOSFET-транзистором (МДП-транзистор основанный на эффекте поля, далее — MOSFET), FinFET-транзистор (полевой транзистор с вертикальным каналом, напоминающим по форме рыбий плавник(fin), далее — FinFET) может быть уменьшен до 20 нм и более, и иметь превосходную производительность. Существует два вида FinFET-транзисторов: КНИ FinFET-транзистор (кремний на изоляторе) и объемный FinFET-транзистор (с изолированным диэлектриком). Объемный FinFET-транзистор построен на основе кремниевых пластин, которые имеют меньшую плотность поверхностных состояний и являются более дешевым решением, чем КНИ пластины, и ко всему прочему осуществляют лучший теплообмен с подложкой в сравнении с КНИ FinFET-транзистором. Здесь описываются основные принципы проектирования объемных FinFET-транзисторов на 14 нм узле, также сравниваются объемный и КНИ FinFET-транзисторы с точки зрения масштабируемости, паразитной емкости и тепловыделения. Рассматривается уменьшение тока стока вследствие паразитного сопротивления в истоке (S) и стоке (D). Колебание тока стока под действием ловушки одного заряда изучено в аспекте глубины ловушки, позиции ловушки и перколяционного пути. При проектировании 14 нм объемного FinFET-транзистора для подавления нежелательных перекрестных помех между стоком и истоком требуется сквозная пробка, находящаяся на глубине прямо под p-n-переходами истока и стока. Максимальная концентрация пробки должна быть 2–3 × 1018 см−3. Глубина залегания p-n-перехода исток-стока должна быть равна или быть чуть меньше чем высота «плавника», которая определяется от поверхности изоляционного окисла до вершины «плавника». В рамках одинаковой концентрации легирующий примеси и геометрии, оба 14 нм объемный и КНИ FinFET-транзисторы имеют практически одинаковые ВАХ (вольт — амперная характеристика), что означает близкий уровень масштабируемости. Поскольку тонкие «плавники», выступающие из подложки, легко истощаются, распределительная емкость от исток-стока к «плавнику» может быть сведена к аналогичным или даже более низким значениям, чем у КНИ FinFET-транзистора. Для достижения подобной интенсивности теплообмена с подложкой, как в случае с объемным FinFET-транзистором, скрытый оксидный слой в КНИ FinFET-транзисторе должен иметь толщину 20 нм или меньше, что в свою очередь может привести к нежелательному увеличению паразитной емкости. Площадь контакта между металлическим электродом и областью исток-сток должна быть как можно шире, чтобы уменьшить паразитное сопротивление.

1 Введение

Транзисторы последовательно уменьшались на протяжении многих поколений производственных технологий в результате неуклонного улучшения производительности канала (скорости), плотности интеграции и затрат на функцию (или бит). Длина затвора транзистора уменьшилась с мкм до нескольких десятков нм. Традиционный транзистор в нано масштабе имеет проблему увеличения тока пробоя (IOFF), как одного из короткоканальных эффектов. Методом подавления такого рода коротко-канальных эффектов является уменьшение толщины окисла затвора, но использование тонкого окисла затвора увеличивает утечку тока затвора. Наноразмерные устройства требуют низкого сопротивления, очень мелкой глубины залегания сток-истоковых p-n-переходов, ультратонкого эквивалента толщины подзатворного окисла с использованием сильных диэлектриков и затвора электрода из металла (или силицида) с низким сопротивлением для удовлетворения спецификации ITRS (InternationalTechnologyRoadmapforSemiconductors, Международный план по развитию полупроводниковой технологии). Из-за этих требований, как известно, сокращения объемных МОП(металл-оксид-полупроводник)-транзисторов с планарной структурой каналов за пределами 20 нм практически невозможно. Одним из драйверов развития будущих поколений технологии является структура устройства. Усовершенствованные конструкции устройств включают в себя одно-затворные транзисторы с ультратонкой подложкой кремний на изоляторе (КНИ), и двух/трехзатворные (ДЗ/ТЗ) (многозатворные) транзисторы, которые имеют лучшую масштабируемость устройства, чем классический транзистор с кремниевой подложкой. Таким образом, будет необходима улучшенная архитектура устройства для достижения преимуществ, полученных от масштабирования устройства в прошлом. Двухзатворные полевые транзисторы, с верхним и нижним, или правым и левым затворами, уже давно признаны за свой потенциал более эффективного контроля ПКЭ (показатели качества электроники). Трехзатворные транзисторы показывают аналогичное поведение, что и двухзатворные, но имеет три электрода на трех поверхностях прямоугольной подложки. Несколько разных структур для Д3 и Т3 полевых транзисторов были разработаны и продемонстрированы экспериментально. На протяжении десятилетий различные виды трехмерных (3D) транзисторов были зарегистрированы. Среди них, FinFET-транзисторы стали преобладающей технологией, поскольку процесс изготовления структуры прибора относительно легок и совместим для обычных плоскоканальных полевых МОП-транзисторов. Корпорация Intel объявила о начале массового производства процессоров на основе 22 нм технологии 3D транзисторов в 2011 году. 3D транзистор назывался трехзатворным или объемным FinFET-транзистором. Объемный FinFET-транзистор был разработан на 14 нм технологическом узле и готов к запуску в массовое производство. Исследования по разработке технологии FinFET продолжается в 10 нм и 7 нм технологическом узле. Однако систематизированного руководства по разработке канала и контакта исток-сток представлено не было. Поэтому в этой главе мы сосредоточимся на анализе внутренней производительности устройства и сопротивлении контакта истока-стока в объемном FinFET-транзисторе на узле 14 нм и предоставим рекомендации по разработке устройства.

2 SOI иBulkFinFET-транзисторы

Прежде всего, основные свойства КНИ и объемных FinFET-транзисторов кратко объясняются в этом разделе. FinFET-транзисторы кажутся очень перспективными для будущего КМОП (комплементарная структура металл-оксид-полупроводник)-технологии, включая логику и приложения памяти. Как упоминалось во введении, FinFET-транзисторы имеют двух-затворную структуру, обеспечивающую хорошие характеристики уменьшения масштаба и высокую производительность. FinFET-транзисторы были в разработке для различных приложений, таких как высокоскоростные цифровые интегральные схемы (ИС), аналоговые микросхемы, SRAMs, флэш-память, и DRAMs.

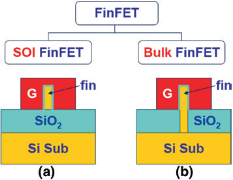

FinFET-транзисторы были известны большинству из нас тем, что изготавливались на КНИ пластинах в конце 1990-х и начале 2000-х годов, а в основном на КНИ МОП-транзисторах. Когда двухзатворные транзисторы были впервые опубликованы, они в основном были продемонстрированы на КНИ подложках, чтобы преодолеть проблемы, связанные с коротко-канальным эффектом. FinFET-транзисторы, построенные на КНИ пластине, называются КНИ FinFET-транзисторы. Эти устройства, как известно, имеют преимущества в простоте изготовления и масштабируемости, поэтому не требуется изоляция неглубоких траншей, и они не имеют канала утечки на глубине рядом с сток-истоковыми p-n-переходами. Данные КНИ устройства обычно применяются для высокоскоростных схем из-за их малой паразитной емкости. В общем, свободная часть КНИ транзистора, включая одно- и двух-затворные устройства, могут иметь проблемы в зависимости от степени легирования, толщины пленки кремния и условий смещения. КНИ пластины имеют более высокую стоимость и более высокую плотность поверхностных состояний, чем пластины объемного кремния. Обратите внимание, что выделяющееся в канале КНИ полевых транзисторов тепло не может легко рассеиваться в подложке из-за глубокого скрытого оксидного слоя с очень плохим теплообменом. Переход с обычных планарных МОП-транзисторов к КНИ FinFET-транзисторам означает не только активное разделение на узкие и обедненные каналы, но также и переход с традиционных четырехтерминальных устройств на трехтерминальные. Следовательно, трехтерминальная характеристика сужает возможности эксплуатации цепи. Поэтому было бы более целесообразным рассмотреть четырехтерминальный FinFET-транзистор, получаемый путем соединения «плавника» непосредственно с кремниевой подложкой. Четырехтерминальные FinFET-транзисторы, построенные на основе пластин объемного кремния, называются FinFET-транзисторами со связанным «плавником», или предпочтительней — объемный FinFET-транзистор. Ф. Л. Ян и соавторы называют МОП-транзистор как omegaFET-транзистор, как сообщало в 2002 IEDM из-за того, что структура затвора похожа на Ω. Чтобы отличать FinFET-транзистор со связанным «плавником» от КНИ FinFET-транзистора и omegaFET-транзистор друг от друга, мы назвали FinFET-транзистор со связанным «плавником» как объемный FinFET-транзистор. Краткое описание классификации технологии FinFET приводится на рис. 1, где показаны поперечные сечения КНИ и объемных FinFET-транзисторов с отрезка «плавника». Тело — “плавник” в КНИ и объемных FinFET-транзисторах размещается и привязано к подложке соответственно. «G» обозначает электрод затвора. Объемные FinFET-транзисторы ближе для конструкторов IC, чем трехтерминальные полевые транзисторы, а также шаги изготовления устройств, совместимых с обычными планарными каналами КМОП устройств, изготовленных на пластине объемного кремния. Трехмерная схема объемного FinFET-транзистора показана на рис. 2.

Рис. 1. Классификация FinFET-транзисторов и поперечное сечение КНИ(a) и объемного(b) FinFET-транзисторов

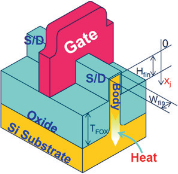

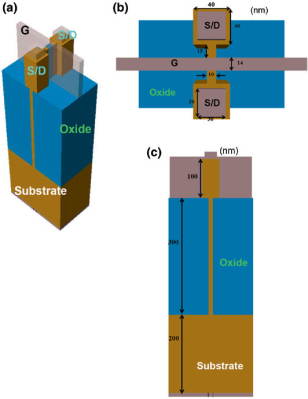

Рис. 2. Трехмерная схема объемного FinFET-транзистора. Hfin и Wfin высота и ширина «плавника» соответственно. TFOX — толщина защитного окисла. xj — глубина залегания p-n-перехода

Здесь Wfinи Hfin обозначаютширину и высоту «плавника» соответственно. Высота «плавника» определяется как высота от поверхности области изоляции оксида к верхней части тела — «плавник». TFOX представляет собой толщину защитного окисла для изоляции устройства. Глубина сток-истоковых p-n-переходов представлена как xj. Тепло, генерируемое в канале, может быть передано к подложке через тело — “плавник”, которое соединено с подложкой. Конструкция объемных FinFET-транзисторов устраняет проблемы, связанные с КНИ FinFET-транзисторами, такие как высокая стоимость пластин, высокая плотность поверхностных состояний, эффект плавающего тела и плохое рассеивание тепла. Кроме того, они сохраняют практически одинаковую масштабируемость КНИ FinFET-транзисторов, обладая лучшими характеристиками тепловыделения. Ключевые свойства объемных FinFET-транзисторов будут подробно описаны в главе о конструировании устройства на 14 нм узле, а затем в сравнении с КНИ FinFET-транзисторами.

Рис. 3. Трехмерная схема 14 нм объемного FinFET-транзистора (a). Вид транзистора сверху(b). Длина затвора Lg = 14 нм, ширина «плавника» Wfin = 10 нм. Площадь контакта к стоку и истоку 40 × 40 нм2. Поперечный срез вдоль истока или стока вдоль канала (с). Высота «плавника» Hfin = 100 нм, толщина защитного окисла TFOX = 300 нм. Толщина оксида на затворе 1 нм. Исток и стоки равномерно легированы примесью с концентрацией 5 × 1020 см-3. Боковые поверхности профиля тела — «плавник» внутри защитного окисла расположены вертикально для простоты моделирования

3.1 Влияние локального легирования профиля на тело— “плавник”

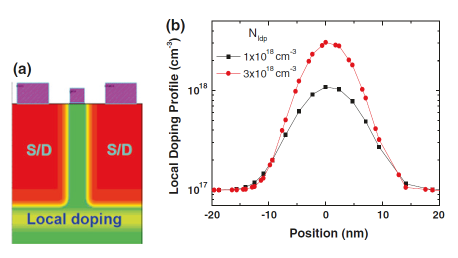

Локальное легирование объемного FinFET-транзистора требуется для подавления нежелательного объемного смыкания рядом с сток-истоковыми p-n-переходами на глубине xj. В КНИ FinFET-транзисторе этот тип легирования не требуется, потому что скрытый оксидный слой эффективно подавляет смыкание. Рис. 4а показывает разрез вдоль длины канала объемного FinFET-транзистора в поперечном сечении. Локальное легирование проводится в нижней части области сток-исток и называется сквозной пробкой. Важными параметрами являются максимальная концентрация легирования и стандартное отклонение локального легирования. На рис. 4b показан пример профиля локального легирования, где Nldp выступает в качестве максимальной концентрации легирования сквозной пробки. В этой главе рассматривается стандартное отклонение легирующего профиля в диапазоне от ~ 8 нм, зависящее от способа обработки вертикально локализованного профиля легирования.

Рис. 4. Поперечное сечение объемного FinFET — транзистора вдоль длины канала. Локальное легирование проводится буквально рядом со дном областей стока и истока (a). Пример локального легирования профиля для подавления нежелательных перекрестных помех (b). Пиковое положение установлено на 0 нм. Nldp — пик концентрации легирующей примеси. В данном случае, концентрация легирующей примеси в теле — «плавник» была установлена на отметке 1 × 1017 см-3

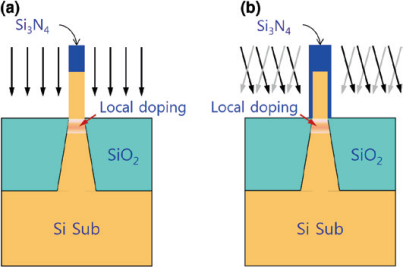

Предложен новый метод формирования сквозной пробки с использованием бокового легирования с помощью разбрасывания ионов из области изоляции (SiO2). В этой технологии, ионы для сквозной пробки имплантируют в область изоляции под углом 0°. Имплантированные ионы распространены в области изоляции, и некоторые из ионов, в результате локализированного легирования, рассеяно и латерально проникают в тело — “плавник”. Ранее имплантированные в область изоляции ионы формируются по обеим сторонам вертикального «плавника» и верхней жесткой маски (Si3N4), сформированной на «плавнике». На рис. 5a изображен поперечный разрез объясняющий имплантацию в изоляционный оксид под углом 0°, а также профиль «плавника», состоящий из двух частей: вертикальное тело — “плавник”, где формируется канал, и коническое тело — “плавник”, в которой ширина тела увеличивается по мере приближения к подложке. На рис. 5 угол имплантации слегка наклонен, а жесткая маска (слой из нитрида, в данном случае Si3N4) формируется на обеих сторонах «плавника», выступающего из оксида изоляции. Поскольку слой нитрида более устойчив к проникновению имплантированных ионов, чем слой SiO2, местная область легирования может быть эффективно сформирована, используя метод, показанный на рис. 5b. Если легирование для сквозной пробки распределяется по вертикали в «плавнике», где формируется канал, пороговое напряжение будет увеличено, что будет причиной деградации управляемости тока за счет увеличения рассеяния примесей. В этом случае имело место бы изменение порогового напряжения из-за случайных колебаний легирования. Таким образом, важно, чтобы профиль легирования был локализован вертикально для подавления смыкания.

Рис. 5. Поперечное сечение объемного FinFET — транзистора вдоль длины канала. Ионная имплантация проводилась под углом 0°(a) и под небольшим углом (b)

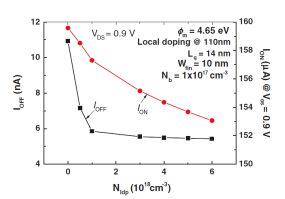

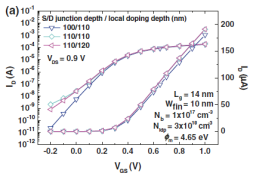

Максимальная концентрация легирования (Nldp) сквозной пробки исследуется с точки зрения характеристик тока стока. Рис. 6 показывает поведение токов ION и IOFFс концентрацией Nldp в 14 нм технологии FinFET на зафиксированной высоте «плавника» Hfin = 100 нм. Толщина оксида затвора в моделируемых структурах составляет 1 нм. Значение максимальной концентрации легирования составляет 110 нм, а глубин p-n-перехода истока (или стока) составляет 100 нм. Как можно увидеть на рисунке, при увеличении Nldp от 0 до 6 × 1018 см-3, ION медленно уменьшается на 4 %. Тем не менее, ток IOFF демонстрирует значительное снижение с 11 до 6 нА, при увеличении Nldp от 0 до 6 × 1018 см-3, после чего происходит только небольшое снижение IOFF при дальнейшем увеличении Nldp. Как следует из рисунка, значения Nldp выше 1 × 1018 см-3,могут считаться приемлемыми. Однако, если процесс ограничен и емкость перехода между истоком (или стоком) к подложке просчитана, то концентрация Nldp = 2–3 × 1018 см-3 — вполне обоснованное решение. Обсудим влияние значения максимальной концентрации легирования путем изменения глубины залегания p-n-перехода стока и истока xj. На рис. 7a показаны характеристики ID — IGS технологии 14 нм FinFET в зависимости от глубины залегания p-n-перехода истока (или стока) и значение максимальной локальной концентрации легирования (эквивалент локальной глубины легирования). Смещение стока установлено в 0,9 В. Значения Hfin, Wfin и Nldpсоставляют 100 нм, 10 нм и 3 × 1018 см-3 соответственно.

Рис. 6. Токи включения ION и выключения IOFF в 14 нм FinFET-транзисторе

На этом рисунке представлено равномерное легирование тела Nb, которое будет рассмотрено в следующем разделе, предположительно составляет 1 × 1017 см-3. Работа выхода электрода затвора (φm) составляет 4,65 эВ. Три разных случая показывают практически тот же ток ION, но с небольшими перепадами примерно в 4 раза относительно значений тока IOFF. Символы перевернутого треугольника описывают кривую отношения ID к VGSв технологии 14 нм FinFET при значениях xj= 100, максимальной концентрации равной 110 нм и при фиксированной Hfin= 100 нм. Если значение xjувеличивается до 110 нм при фиксированной Hfin= 100 нм, происходит значительное увеличение IOFF независимо от значения максимальной локальной концентрации легирования. Результаты показывают, что значение xj должно быть меньше, чем Hfin, поскольку нежелательные перекрестные помехи между истоком и стоком в таких условиях могут быть эффективно подавлены электрическим полем электрода затвора. На рисунке 7b показаны результаты, аналогичные полученным в рис. 7a в виде функции xj, при фиксированном Hfin = 100 нм. Кривая отношения ID к VGSв технологии 14 нм FinFET является обоснованной, поскольку смыкание подавляется электрическим полем от смещения затвора. Однако при увеличении xj до 110 нм происходит значительное увеличение (как показано треугольными символами). Обратите внимание, что уменьшение xj вызывает незначительное уменьшение ION, потому что эффективная ширина канала уменьшается.

Рис. 7. Исследование положения пика локального легирования и параметра xj (a). Изменение параметра xj при фиксированном положении пика локального легирования (b)

3.2 Влияние легирования на тело— “плавник”

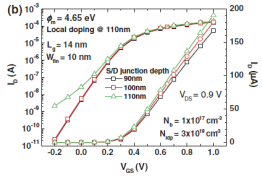

Легирующая концентрация примеси в теле — “плавник” является ключевым параметром, влияющим на проектирование подпорогового наклона (SS), снижение сток-индуцированного барьера (DIBL) и подвижность носителей. С точки зрения подвижности носителей, легирование тела должно быть настолько низким, насколько это возможно. Тем не менее, уменьшение легирования тела вызывает увеличение DIBL и SS, как показано на рис. 8. На чертеже легирование тела предполагается однородным. По мере увеличения легирования тела с 1 × 1017 см-3 до 4 × 1017 см-3 ION уменьшается примерно на 5 %, в то время как IOFF уменьшается значительней (~ 40 %).

Рис. 8. Подпороговый размах напряжения (SS) и снижение потенциального барьера (DIBL) в 14 нм FinFET-транзисторе как параметры легирующей концентрации примеси в «плавнике». В данном случае VDS = 0.9 В. Предполагается что легирование «плавника» равномерно

Обратите внимание, что Vth сохраняет практически одинаковые значения для разных концентраций легирования тела, потому что это в основном определяется работой выхода электрода затвора (4,65 эВ). Когда легирование тела увеличивается с 1 × 1017 до 2 × 1017 см-3, то происходит значительное снижение IOFF. На рис. 8 можно увидеть, как по мере увеличения концентрации тела с 1 × 1017 до 4 × 1017 см-3, DIBL на токе ID = 10–7А меняется в пределах 2,5 %, в то время как SS при VDS меняется примерно на 2 %. Принимая во внимание все факторы, упомянутые выше, легирование тела в 2–3 × 1017 см-3 вполне обоснованно.

3.3 Влияние расстояния между p-n-переходами

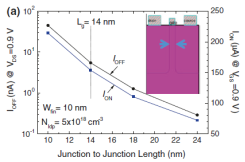

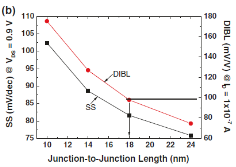

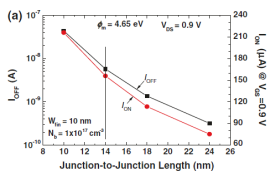

Теперь рассматривается влияние расстояния между p-n-переходами стока и истока (расстояние между p-n-переходами) при фиксированной длине канала в 14 нм. На рис. 9а показан вид в поперечном разрезе, выполненном по длине канала объемного FinFET-транзистора. Стрелки необходимы, чтобы показать расстояние между p-n-переходами истока и стока(расстояние между p-n-переходами), которое в данном примере 14 нм. На этом рисунке легирование тела Nb = 1 × 1017 см-3. Если взглянуть на рис. 9а, то можно заметить, что ION и IOFF значительно уменьшаются при увеличении расстояния. Особенно заметные изменения (до 100 раз) можно наблюдать с током IOFF при изменении расстояния с 10 до 24 нм. Если длина больше, чем 14 нм, можно сказать, что исток и сток отрицательно перекрываются. При длине 14 нм VGS и VDS по 0,9 В ION ~ 728 мкA/мкм, а при VGS = 0 и VDS =0,9 IOFF = 26 нA/мкм. Обратите внимание, что в данной симуляции были применены только модели дрейфа и диффузии. На рис. 9b показаны характеристики SS и DIBL в зависимости от расстояния. С увеличением расстояния между p-n-переходами характеристики SS и DIBL значительно улучшились. Тем не менее, можно заметить уменьшение ION и IOFF по мере увеличения расстояния. Если DIBL сохраняется при 100 мВ/В, расстояние должно быть больше 18 нм при легировании тела в 1 × 1017 см-3. При умеренном легировании тела в 2 -3 × 1017 см-3, расстояние может быть уменьшено до ~ 14 нм. Если нет никакого упоминания о расстоянии между переходами, то оно по умолчанию равно 14 нм.

Рис. 9. Изменение токов ION и IOFF в зависимости от расстояния между стоком и истоком (a). Изменение SS и DIBL в зависимости от расстояния (b). Рисунок на графике (a) представляет собой поперечное сечение вдоль длины канала. Стрелки показывают длину (14 нм)

3.4 Влияние ширины «плавника»

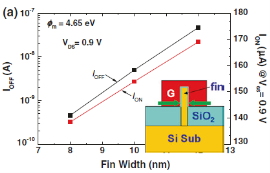

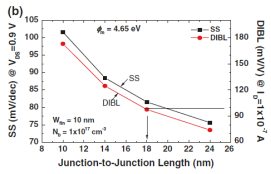

Контроль ширины «плавника» (Wfin) очень важен при заданном угле, поскольку ширина значительно влияет на короткоканальный эффект. Ширина «плавника» определяется двумя стрелками на рис. 10а. При уменьшении ширины «плавника» с 12 до 8 нм IONуменьшается на 18 %, в то время как IOFF уменьшается примерно в 100 раз, что показано на рис. 10а. Таким образом, IOFF очень чувствителен к ширине «плавника», которая должна быть контролируемой для поддержания ограниченного распределения IOFF.

Рис. 10. Изменение токов ION и IOFF в зависимости от ширины «плавника» (a). Изменение SS и DIBL в зависимости от ширины (b). Рисунок на графике (a) представляет собой поперечное сечение вдоль длины канала. Стрелки показывают ширину «плавника». Длина p-n-перехода 14 нм. Высота плавника и глубина залегания p-n-перехода 100 нм соответственно. Ток IONполучен при VGS = 0.9 В, VDS = 0.9 В. Ток IOFFполучен при VGS = 0, VDS = 0.9 В

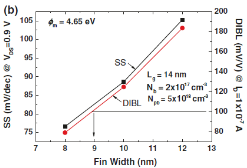

Обратите внимание на общую эффективную ширину канала (2 × Hfin + Wfin), уменьшающуюся с 212 до 208 нм, в то время как Wfin уменьшается с 12 до 8 нм. Снижение общей ширины чуть менее 2 % от Wfin. Причиной снижения ION в основном можно отнести к снижению Vth вместе с уменьшением Wfin. И наоборот, снижение IOFF с уменьшением Wfin можно объяснить двумя причинами: снижением Vth и увеличением SS с уменьшением Wfin. Vth определяемое на ID как 1 мкA/мкм уменьшается на 0,14 В вследствие уменьшения Wfin с 12 до 8 нм. На рис. 10b можно увидеть изменение SS и DIBL с Wfin. По мере того как уменьшается Wfin с 12 до 8 нм, SS уменьшается со 106 до 77 мВ/дек, DIBL снижается с 183 до 80 мВ/В. Таким образом, Wfin также оказывает значительное влияние на SS и DIBL. Значение Wfin примерно 9нм дает DIBL 100 мВ/В при заданной концентрации тела 2 × 1017 см-3. Если мы увеличим концентрацию легирования тела до 2,5–3 × 1017 см-3, то DIBL уменьшится, а значение Wfin должно быть около 10 нм чтобы обеспечить DIBL в 100 мВ/В.

4. Конструирование 14 нм КНИ FinFET-транзистора

В разделе 3 мы исследовали ключевые факторы конструирования 14 нм объемных FinFET-транзисторов. Теперь мы рассмотрим производительность устройства 14 нм КНИ FinFET-транзистор и сравним основные свойства КНИ FinFET-транзистора с объемными FinFET-транзисторами.

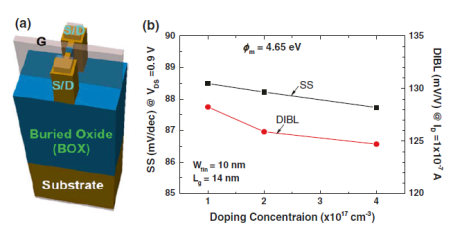

4.1 Влияние легирования на тело— “плавник”

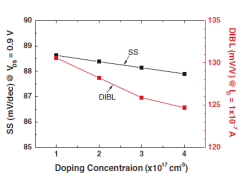

В КНИ FinFET-транзисторах нет необходимости для локального легирования, которое требуется в объемных FinFET-транзисторах для подавления смыкания между истоком и стоком, так как он содержит скрытый оксидный слой (BOX), расположенный под телом — «плавник», где сформированы канал и контакт исток-сток. На рис. 11а представлена трехмерная схема КНИ FinFET-транзистора. За исключением внедренного оксида, структура устройства полностью совпадает с объемным FinFET-транзистором. Толщина скрытого оксидного слоя составляет 300 нм. На рис. 11bSS и DIBL 14 нм КНИ FinFET-транзистора представлены как зависимость легирования «плавника» и концентрации(Nb). При увеличении Nb с 1 × 1017 до 4 × 1017 см-3, SS уменьшается с 88,5 до 87,7 мВ / дек, в то время как DIBL уменьшается с 128,2 до 124,7 мВ /В. Эти параметры изменяются незначительно относительно Nb, и вполне аналогичны таковым из 14nm объемного FinFET-транзистора на рис. 8.

4.2 Влияние расстояния между p-n-переходами

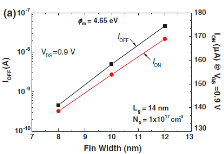

Влияние расстояния между p-n-переходами на производительность в 14 нм КНИ FinFET-транзисторе исследуется на рис.12. На рис. 12 легирование тела Nb = 1 × 1017 см-3. При рассмотрении рис.12 можно увидеть, что ION и IOFF значительно уменьшаются с увеличением расстояния. Особенно можно наблюдать значительные изменения IOFF, до 100 раз при изменении длины с 10 до 24нм. При длине 14 нм, когда VGS и VDS по 0,9 В, ION ~ 730 мкA/мкм, а при VGS = 0 и VDS = 0,9 IOFF = 26 нA/мкм. Обратите внимание, что в данной симуляции были применены только модели дрейфа и диффузии. Показатели IONи IOFF КНИ FinFET-транзистора очень похожи на соответствующие показатели объемного FinFET-транзистора, что показано на рис. 9а. На рис. 12b показаны характеристики SS и DIBL IOFF 14 нм КНИ FinFET-транзистора в зависимости от расстояния. С увеличением расстояния между p-n-переходами характеристики SS и DIBL значительно улучшилось. Тем не менее, можно заметить уменьшение ION и IOFF, по мере увеличения расстояния. Если DIBL сохраняется при 100 мВ/В, расстояние должно быть больше 18 нм, при легировании тела в 1 × 1017 см-3. При умеренном легировании тела в 2–3 × 1017 см-3, расстояние может быть уменьшено до ~ 14 нм. Таким образом, 14 нм КНИ FinFET-транзистор показывает почти такую же производительность, что и 14 нм объемный FinFET-транзистор.

Рис. 11. Трехмерная схема 14 нм КНИ FinFET-транзистора (a). Структура устройства идентична 14 нм FinFET-транзистору, представленному на рис. 3. Единственная разница, это скрытый оксид (BOX) в КНИ FinFET-транзисторе. Толщина скрытого оксидного слоя 300 нм. Изменение SS и DIBL в зависимости от концентрации легирующей примеси в «плавнике» (b). Длина p-n-перехода 14 нм. Высота плавника и глубина залегания p-n-перехода 100 нм соответственно. Изменение SS получено при VDS = 0.9 В

Рис. 12. Изменение токов ION и IOFF в зависимости от расстояния между стоком и истоком (a). Изменение SS и DIBL в зависимости от расстояния (b). Ток IONполучен при VGS = 0.9 В, VDS = 0.9 В. Ток IOFFполучен при VGS = 0, VDS = 0.9 В. Высота плавника и глубина залегания p-n-перехода 100 нм соответственно. Изменение SS получено при VDS = 0.9 В

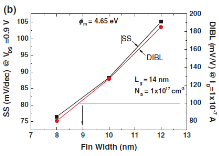

4.3 Влияние ширины «плавника»

Как и в случае с объемным FinFET-транзистором, влияние ширины тела — «плавник» в 14 нм КНИ FinFET-транзисторе изучается в этом разделе. При уменьшении ширины «плавника» с 12 до 8 нм, IONуменьшается на 18 %, в то время как IOFF уменьшается примерно в 100 раз, что показано на рис. 13а.

Рис. 13. Изменение токов ION и IOFF в зависимости от ширины «плавника» (a). Изменение SS и DIBL в зависимости от ширины (b). Рисунок на графике (a) представляет собой поперечное сечение вдоль длины канала. Стрелки показывают ширину «плавника». Длина p-n-перехода 14 нм. Высота «плавника» и глубина залегания p-n-перехода 100 нм соответственно. Ток IONполучен при VGS = 0.9 В, VDS = 0.9 В. Ток IOFFполучен при VGS = 0, VDS = 0.9 В

Таким образом, IOFF очень чувствителен к ширине «плавника», которая должна быть контролируемой для поддержания ограниченного распределения IOFF. Как описано в разделе 3.4, снижение общей ширины составляет чуть менее 2 % от Wfin. Причиной снижения ION в основном можно отнести к снижению Vth вместе с уменьшением Wfin. И наоборот, снижение IOFF с уменьшением Wfin можно объяснить сопровождающим снижением Vth и увеличение SS. Vth определяемое на ID как 1 мкA/мкм уменьшается на 0,14 В вследствие уменьшения Wfin с 12 до 8 нм. На рис. 10b можно увидеть изменение SS и DIBL с Wfin. По мере того, как уменьшается Wfin с 12 до 8 нм, SS уменьшается со 106 до 77 мВ/дек, DIBL снижается с 183 до 80 мВ/В. Таким образом, Wfin также оказывает значительное влияние на SS и DIBL. Значение Wfin примерно 9 нм дает DIBL 100 мВ/В при заданной концентрации тела 1 × 1017 см-3. Если мы увеличим концентрацию легирования тела до 2,5–3 × 1017 см-3, то DIBL уменьшится, а значение Wfin должно быть около 10 нм чтобы обеспечить DIBL в 100 мВ/В. Все анализы, проведенные для объемного FinFET-транзистора точно такие же, как и для КНИ FinFET-транзистора.

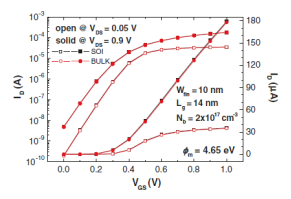

4.4 Сравнение зависимости ID–VGS для КНИ иобъемного FinFET-транзисторов В этом разделе мы сравниваем кривые зависимости ID–VGS для КНИ и объемных FinFET-транзисторов. Как уже упоминалось выше, они имеют очень похожую структуру, за исключением того, что объемный FinFET-транзистор имеет локальное легирование, расположенное на глубине под p-n-переходами истока и стока, в то время как КНИ FinFET-транзистор содержит скрытый оксидный слой на месте локального легирования. Высота и ширина «плавника» составляют 100 и 10 нм соответственно. Тело — “плавник” равномерно легированj примесью с концентрацией 2 × 1017 см-3. Как показано на рис. 14, объемный и КНИ FinFET-транзисторы имеют точно такие же I/V характеристики, как показано на графике кругами и квадратами соответственно.

Рис. 14. График изменения ID-VGSв 14 нм объемном (кружки) и КНИ (квадраты) FinFET-транзисторах. Длина p-n-перехода 14 нм. Высота «плавника» и глубина залегания p-n-перехода 100 нм соответственно. Плавник равномерно легирован примесью с концентрацией 2 × 1017 см-3. Толщина оксидной пленки на затворе 1 нм.

Литература:

- Lilienfeld JE (1930) Method and apparatus for controlling electric currents. U. S. Patent 1,745,175 (filed in 1926, issued in 1930)

- Kahng D, Atalla MM (1960) Silicon-silicon dioxide field induced surface devices. Paper presented at the IRE solid-state devices research conference, Pittsburgh, PA, June 1960

- Deal BE (1969) Method of making stable semiconductor devices. U. S. Patent no. 3,426,422, 11 Feb 1969

- Semiconductor Industry Association (SIA) (2013) International technology roadmap for semiconductors, 2013 edn

- Kedzierski J, Xuan P, Subramanian V, Anderson E, Bokor J, King T-J, Hu C (2000) A 20 nm gate-length ultra-thin body p-MOSFET with silicide source/drain. Superlattices Microstruct 28(5):445–452