Память — устройство хранение данных (информации), запоминающее устройство. Физическое устройство, используемое в вычислениях и хранении определённых данных в течение заданного времени. Память является неизменной и незаменимой частью компьютерных устройств, начиная с 1940-х годов.

Ячейка памяти — это минимально-возможный адресуемый элемент памяти (запоминающего устройства). Данная ячейка может иметь различную емкость, длину и число разрядов. Также ячейки памяти присваивается адрес (порядковый номер) с помощью которого происходит обращение команды процессора к памяти.

Можно выделить два основных вида ячеек памяти построенных на полупроводниковых технологиях: (SRAM) — статическая память, не требующая регулярного обновления, (DRAM) — динамическая память, которая нуждается в периодической перезаписи для сохранения информации. Из этого следует, что в основном из статических ячеек памяти организуют кеши, а при помощи динамической памяти — ОЗУ.

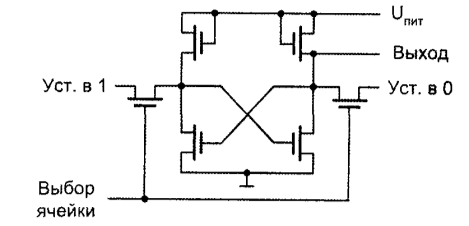

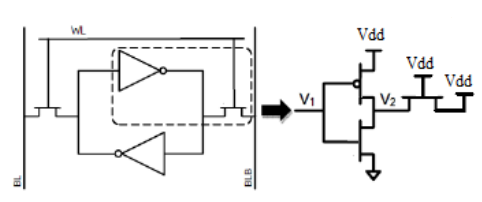

SRAM (static random access memory) — статическая память с произвольным доступом (Рисунок 1). Это полупроводниковая оперативная память, в которой каждый разряд (двоичный или троичный) хранится с положительной обратной связью в схеме, которая в отличии от динамической памяти (DRAM) позволяет поддерживать определенное состояние без регенерации. Однако сохранение данных без перезаписи в SRAM возможно только пока есть питание, из этого следует, что SRAM является энергозависимым типом памяти. С помощью произвольного доступа (RAM — random access memory) возможно осуществлять выбор для записи или чтения любой из битов, в отличие от конструкции памяти с последовательным доступом (SAM — sequential access memory).

Рис. 1. Электрическая схема запоминающего элемента SRAM

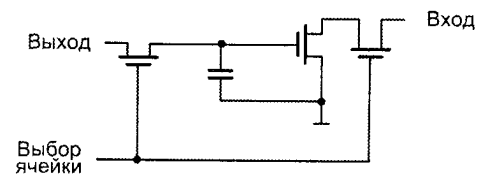

DRAM (dynamic random access memory) — динамическая память с произвольным доступом (Рисунок 2). Это энергозависимая полупроводниковая память, которая имеет произвольный доступ. Данный тип памяти широко используется в качестве оперативной памяти в нынешних компьютерных устройствах, а также для постоянного хранилища данных (информации).

Рис. 2. Электрическая схема запоминающего элемента DRAM

Устройства памяти являются одним из основных компонентов современной электроники. Нынешняя тенденция современных КМОП технологий — это стремление к постоянному уменьшению размеров элементов, снижение энергопотребления интегральных схем. Из этого следует много положительных моментов, однако в связи с уменьшением размеров интегральных компонентов возникает ряд проблем, связанных с технологическим разбросом транзисторных характеристик и линий связи. Данная проблематика в особенности ярко выражается при проектировании устройств памяти.

На Рисунке 1 представлена классическая 6-ти транзисторная ячейка статической памяти. Так как используются одни и те же шины для входной и выходной информации, операцию записи и чтения невозможно выполнить в один момент времени.

Устойчивость работы статических ячеек памяти напрямую зависит от изменения параметров транзисторов и линий их связи, в зависимости от технологии их изготовления. Из-за разбросов технологических параметров следует изменение важных характеристик транзисторов, таких как порог, емкость и различные усилительные свойства.

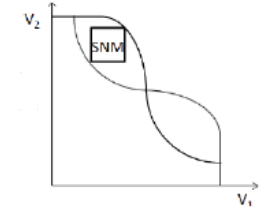

Для характеризации ячеек памяти и оценки их помехоустойчивости водится такой параметр, как статический запас помехоустойчивости (Static Noise Margin — SNM). Что бы определить «SNM» необходимо выполнить наложение графиков передаточных характеристик двух инверторов статической ячейки памяти (Рисунок 3), которые образуют триггер. Сторона квадрата, полученная при наложении двух характеристик, является искомой величиной SNM (Рисунок 4).

Рис. 3. Эквивалентная схема для определения значения SNM

Рис. 4. График передаточных характеристик двух инверторов

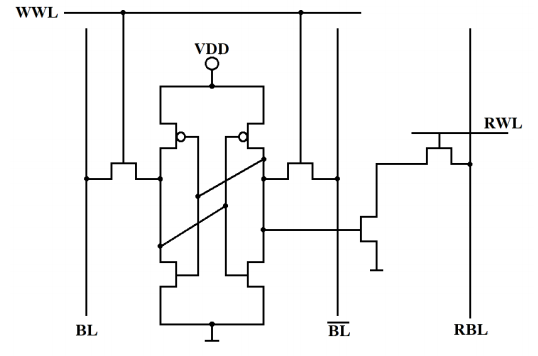

При отсутствии достоверной информации о технологический разбросов параметров во время производства памяти практически невозможно реализовать необходимый запас помехоустойчивости 6-ти транзисторной статической ячейки памяти. Для решения данной проблемы используют 8-ми транзисторную ячейку памяти (Рисунок 5), которая позволяет разделить операции чтения и записи.

Рис. 5. Схема 8-ми транзисторной статической ячейки памяти: RWL — Read Word Line; WL — World Line; BL — Bit Line

Линия WWL управляет затворами двух полевых транзисторов. Линия BL — битовые линии, необходимы для записи данных (в 6-ти транзисторной ячейки памяти данные линии осуществляют как функцию записи, так и функцию чтения). Во время процесса считывания в 8-ми транзисторной ячейке памяти подается сигнал на линию RWL, исходя из того какая информация хранилась в ячейки, мы имеем инверсный сигнал на выходной линии RBL. Запись в данной ячейки памяти реализована таким же образом, как и в 6-ти транзисторной ячейки памяти.

Вывод.

Одна из возможностей достижения быстродействия и стабильности ячеек памяти является разделения портов записи и чтения. Добавление двух транзисторов в 8-ми транзисторной ячейки памяти ведет к значительной прибавки к площади всей памяти, однако это значительно компенсируется улучшением временными параметрами, а также возможностью реализации многопортовой памяти.

Литература:

- Амосов В. В. Схемотехника и средства проектирования цифровых устройств. БХВ-Петербург, 2012.

- Бойко В. И., Гуржий А. Н. Схемотехника электронных систем. Цифровые устройства. БХВ-Петербург, 2012.

- Угрюмов Е. П. Цифровая схемотехника. Учебное пособие для вузов, 2 издание. БХВ-Петербург, 2011.

- Jason Cong. An interconnect centric design flow for nanometer technologies, Proceedings of IEEE, vol. 89, 2009.

- Vjay Gullapalli, Kaijani Shi — Hierarchical design techniques, Synopsys white paper, 2008.