Пути наращивания производительности вычислительных систем.

На данный момент существует несколько способов увеличения производительности вычислительных систем при фиксированном технологическом процессе: увеличение числа процессоров (вычислителей) в системе (например, MainFrame), распределение вычислений в компьютерной сети (например, Кластер), использование сопроцессоров (например, в видео адаптере или в виде отдельно подключаемых устройств, выполняющих специфические «сложные» вычисления).

Использование сопроцессоров и их реализация на различных видах ИС.

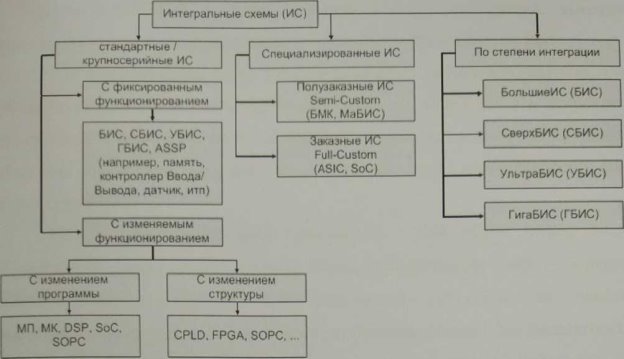

Для фирм, нуждающихся в выполнении сложных вычислений и не готовых тратить огромные средства на приобретение, обслуживание суперкомпьютеров, MainFrame, Кластеров и т. п., хорошим выходом является использование сопроцессоров, т. е. аппаратно- и/или программно-реализованных блоков, предназначенных для выполнения определенной задачи (алгоритма). Сопроцессоры могут быть реализованы на основе различных интегральных схем, перечисленных ниже и представленных на рисунке 1 в виде классификации.

Рис. 1. Классификация интегральных схем

ASIC (Application-Specific Integrated Circuit) — специализированная интегральная схема (ИС) для решения строго конкретной задачи и узкого круга потребителей (один заказчик). Микросхема ASIC имеет узкий круг применения, обусловленный жёстко предопределённым набором её функций, неизменным после выпуска ASIC. Разработчики цифровых ASIC используют HDL для описания функциональности ASIC, а также специальные средства проектирования ASIC.

Недостаток ASIC заключается в очень высокой стоимости разработки, в высоких требованиях к функциональной правильности реализуемого на них устройства. Т. к. ASIC часто изготавливаются в больших количествах, практически нет возможности изменения устройства после выпуска (это нерепрограммируемое устройство), а на устранение дефекта может потребоваться около года, то моделирование и тестирование проекта должно выполняться на всех уровнях детализации при максимально полном тестирующем наборе воздействий.

Достоинство ASIC — очень высокая степень интеграции, высокая производительность по сравнению с остальными описываемыми ИС.

ASSP (Application specific standard product) — специализированная интегральная схема (ИС) для решения строго конкретной задачи и широкого круга потребителей (множество заказчиков). Т. е. отличается от ASIC только объемом заказов и, следовательно, подпадает под классификацию как стандартная ИС.

БМК (Базовые Матричные Кристаллы) = GA (Gate Array), ULA (Uncommited Logic Array), MPGA (Mask Programmable GA) — заранее изготовленная стандартная БИС регулярной структуры на основе повторяющего набора схемных элементов (базовая ячейка) без верхнего(их) сигнального слоя, который разрабатывается заказчиком и наносится на предприятии — изготовителе БМК. БМК программируется технологически, путём нанесения маски соединений последнего слоя металлизации, изготовленной на заказ или полученной от заказчика. Таким образом, стоимость полученного устройства будет меньше стоимости полностью разработанной заказной ИС. При проектировании устройств на основе БМК применяются библиотеки типовых логических элементов и библиотеки функциональных ячеек, разработанные предприятием-изготовителем БМК.

Недостатки БМК:

– Однократное нанесение верхнего сигнального слоя на предприятии- изготовителе БМК, для чего необходима передача топологии сигнального слоя (маски) к изготовителю.

– Неполное использование площади и ресурсов БМК, неоптимальные расположение элементов и линии связи и, следовательно, меньшее быстродействие по сравнению с ASIC.

МаБИС (Матричная БИС) — представляет собой базовые элементы (например, транзисторы), расположенные в узлах прямоугольной решетки, являющейся последовательностью ортогональных проводников. МаБИС — это полностью изготовленная схема на основе БМК.

SoC (System on Chip — Система на Кристалле), SmartCard — ASIC, содержащая полноценный процессор или несколько процессоров, блоки памяти, включая ROM, RAM, EEPROM, Flash, развитую систему Ввода/Вывода и другие крупные блоки. Такие системы дороги в проектировании и в производстве. Поэтому экономически целесообразно может быть только массовое производство таких схем.

SoPC (System on Programmable Chip) — ПЛИС (см. далее), содержащая полноценный процессор или несколько процессоров и/или блоки памяти, включая ROM, RAM, EEPROM, Flash и/или развитую систему Ввода/Вывода и/или другие крупные блоки. Эти блоки могут быть заранее включены в ПЛИС, являясь их неотъемлемой частью (Hard ядро), а могут быть частью проекта, сконфигурированного/«прошитого» на ПЛИС (Soft ядро). Подробнее о видах IP ядер смотри ниже.

Массовость производства SoPC обеспечивается универсальностью системы. Универсальность же обеспечивается возможностью репрограммирования всей системы (изменение программы, конфигурирование ПЛИС).

SoC и SoPC имеют наиболее высокие показатели быстродействия, степени интеграции, а также технические и экономические качественные показатели.

Микросхемы уровня SoC, SoPC применяются для решения сложных задач. Их проектирование требует больших затрат на проектирование / разработку, тестирование.

МП (Микропроцессор) — процессор, выполненный в виде одной либо нескольких взаимосвязанных интегральных схем. Микропроцессор состоит из цепей управления, регистров, сумматоров, счетчиков команд и очень быстрой памяти малого объема. МП характеризуются областью применения, архитектурой (организация памяти и шин, конвейерной обработкой, предсказание переходов, очередью команд на выполнение и др.), быстродействием, способами адресации, набором и архитектурой (аккумуляторная-регистровая — RISC, CISC, VLIW и стековая — ROSC) выполняемых команд, параметрами надежности (наработка на отказ и др.), и многими другими особенностями.

МК (Микроконтроллер) = MCU (Micro Controller Unit) — разновидность микропроцессорных устройств (микро-ЭВМ), ориентированных на реализацию алгоритмов управления техническими устройствами и технологическими процессами.

Типичный микроконтроллер сочетает в себе функции низкопроизводительного микропроцессора (порядка десятков MГц) и периферийных устройств с различными встроенными интерфейсами (I2C, UART, SPI, JTAG, USB и т. д.). Также МК может содержать небольших размеров ОЗУ (Оперативное запоминающее устройство) = RAM (Random access memory) и ПЗУ (Постоянное запоминающее устройство) = ROM (Read only memory).

По сути, МК — однокристальный компьютер, способный выполнять только простые задачи. Работа МК контролируется его программой и основана на использовании датчиков (периферийных устройств) и обработке прерываний от внешних устройств (от системы ввода/вывода, внешних линий прерываний), от внутренних устройств (таймеров, АЛУ, АЦП и т. д.).

Недостаток МК — они обладают меньшей производительностью по сравнению с аппаратными решениями (ASIC, ПЛИС и др.). Но функциональность МК может быть легко изменена (исправлена) с помощью изменения программы, выполняемой МК.

DSP (Digital Signal Processor) = ЦСП (Цифровой Сигнальный Процессор) — специализированный МП/МК, предназначенный для цифровой обработки сигналов (обычно в реальном масштабе времени). Характеризуется массовым параллелизмом, конвейерной обработкой, гарантированным временем выполнения операций. Различаются по набору встроенных устройств, быстродействию, архитектуре, типу выполняемых арифметических операций (с фиксированной/плавающей точкой), разрядности данных и адресов, организации памяти, поддерживаемым интерфейсам с внешними устройствами, характеристикам надежности, энергопотребления, количеству пользовательских выводов и многим другим.

Недостаток DSP — из-за большого набора вычислительных устройств, поддержки конвейерной обработки и других факторов стоимость DSP выше, чем у МК, хотя управление DSP тоже программное.

ПЛИС — интегральная схема регулярной структуры на основе логических ячеек (Logic cell), но с программируемыми связями и элементами памяти, позволяющая реализовывать на ней различные устройства. В отличие от БМК, ПЛИС выпускаются полностью готовыми, в них реализованы уже не только логические элементы, триггеры, мультиплексоры и т. п., но и связи внутри логических ячеек. Логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования / конфигурирования).

ПЛИС бывают однократно программируемыми (на основе перемычек типа antifuse, на основе EPROM-OTP (Erasable Programmable ROM — One Time Programmable)) и многократно программируемыми (на основе EPROM, EEPROM (Electrically Erasable Programmable ROM), на основе SRAM (Static RAM)).

Благодаря регулярной структуре ПЛИС и сбалансированному составу логической ячейки (см. далее) ПЛИС реализация проектов на ПЛИС происходит с уровнем интеграции, близким к максимальному (для данной ПЛИС).

Недостатки ПЛИС:

– Более низкая скорость работы ПЛИС в сравнении с ASIC.

– Нерентабельность использования в крупносерийном производстве.

– Меньшая степень использования площади кристалла по сравнению с БМК и, тем более, ASIC. Т. к. часть кристалла ПЛИС занимает схема конфигурирования (SRAM — ячейки, память EEPROM и т. п.)

Достоинства ПЛИС:

– Простота и малое время проектирования (высокоуровневое проектирование в удобной среде разработки, с возможностью тестирования устройства в виде временных диаграмм реакции на определенное входное воздействие).

– Низкая стоимость разработки (т. к. ПЛИС является полностью стандартным продуктом).

– Более низкая стоимость в сравнении с использованием отдельных интегральных схем средней степени интеграции.

– Более продолжительное обращение продукта на рынке за счет возможности репрограммирования.

– Возможность создания динамически реконфигурируемых устройств (само-реконфигурирование / частичное реконфигурирование).

Альтернативой ПЛИС являются: БМК, требующие заводского производственного процесса для программирования; ASIC — специализированные заказные ИС (интегральные схемы), которые при мелкосерийном и единичном производстве существенно дороже; специализированные компьютеры, процессоры (например, цифровой сигнальный процессор) или микроконтроллеры, которые из-за программного способа реализации алгоритмов медленнее ПЛИС.

Снижение трудоемкости проектирования, параметры для оценки логической сложности ИСПС.

Необходимость снижения трудоемкости проектирования и, следовательно, стоимости проектирования — важная задача микроэлектроники, одним из путей решения которой стало создание библиотек схемных решений. Начало этому движению положили библиотеки функциональных блоков для БМК, которые разрабатывались производителями этих БМК. Сейчас изготовлением таких готовых решений стали заниматься и специализированные фирмы, причем библиотечные блоки могут быть различной сложности, вплоть до МП/МК и ЦОС-ядер.

Библиотечные блоки для ИС программируемой логики (ИСПЛ) делятся на классы:

– Soft ядра или виртуальные компоненты — файл-описание на каком-либо HDL, который можно интегрировать в разрабатываемый проект.

– Firm ядра — то же самое, что и Soft ядра, но с полностью или частично выполненной разводкой линий связей на кристалле.

– Hard ядра — уже реализованные на кристалле и оптимизированные под конкретный кристалл области с фиксированными, далее не программируемыми функциями (как ASIC, что обеспечивает более высокую производительность (на 20–50 %), а отсутствие средств конфигурирования приводит к значительной экономии, занимаемой Hard ядром площади кристалла (в несколько раз), по сравнению с Soft и Firm ядрами). Но функции Hard ядра строго определены, что снижает универсальность схемы.

Hard ядра жестко фиксированы в кристалле микросхемы (МС) и приобретаются в её составе. Soft ядра и Firm ядра приобретаются самостоятельно и являются единицами интеллектуальной собственности, в следствие чего получили название IP (Intellectual Properties).

Чем выше процент синтезируемой части МС, тем больший контроль над реализацией получает пользователь/разработчик проекта, но тем больше блоков при этом теряют оптимальность своих параметров.

Для оценки логической сложности БМК, ПЛИС и синтезируемой части SoPC используется понятие «эквивалентный вентиль» (далее ЭВ) — группа элементов, соответствующая возможности реализации логической функции вентиля (обычно это двухвходовой элемент И-НЕ, либо ИЛИ-HE). Также для сравнения ПЛИС используется понятие «логическая ячейка» или «логический элемент» (ЛЯ — Logic cell, LC, или ЛЭ — Logic element, LE), состоящие из одной 4-входовой LUT (Look-up table — таблица подстановки или функциональный генератор), запоминающего элемента (Flip-Flop — триггер, далее FF), логики ускоренного переноса.

HDL: Verilog и VHDL.

Для разработки устройств на основе БМК, ПЛИС, ASIC, SoPC используются HDL (Flardware Description Language — языки описания аппаратуры), такие как VFIDL, Verilog AHDL и др. (см. ниже), а также специальные среды проектирования (для ПЛИС — Xilinx ISE, Altera Quartus II и т. д.), подробнее о них см. ниже. Эти среды проектирования поддерживают описание проекта на различных уровнях его детализации (от уровня регистровых передач и функционально-логического до вентильного и схемотехнического), позволяют моделировать поведение устройства даже с учетом задержек, использовать в описании аппаратуры конечные автоматы и даже алгоритмы.

При описании устройства на VHDL и Verilog можно использовать различные стили:

– Поведенческий или алгоритмический стиль — при котором описание устройства представляется в виде причинно-следственных связей между событиями на входах и выходах устройства, без уточнения структуры.

– Структурный стиль — при котором устройство представляется в виде иерархии взаимодействующих элементов.

– Потоковый стиль — который основывается на использовании логических уравнений, каждое из которых преобразует один или несколько входных информационных потоков в выходные потоки.

– На практике при описании сложных устройств часто используется комбинация указанных стилей.

Литература:

- Классификация // StudFiles. URL: http://www.studfiles.ru/preview/2527421/ (дата обращения: 01.04.2017).

- Методы увеличения вычислительной производительности // IXBT.com. URL: http://www.ixbt.com/cpu/cpuspeed.shtml (дата обращения: 01.04.2017).

- ASIC (Application Specific Integrated Circuit) // INFLIB.RU. URL: http://inflib.ru/index2.php?option=com_content&task=view&id=1536&pop=1&page=0&Itemid=29 (дата обращения: 02.04.2017).

- Базовые матричные кристаллы (вентильные матрицы) // ЛЕКЦИЯ. URL: http://lektsia.com/2x3bfe.html (дата обращения: 02.04.2017).

- Тема 14. Программируемые логические интегральные схемы // СтудопедиЯ. URL: http://studopedia.ru/2_10602_tema--programmiruemie-logicheskie-integralnie-shemi.html (дата обращения: 02.04.2017).

- Особенности языков описания архитектуры Verilog и VHDL // PARALLEL.RU. URL: https://parallel.ru/fpga/hdl.html (дата обращения: 01.04.2017).

- Поляков А,К,. Языки VHDL и VERILOG в проектировании цифровой аппаратуры. —: Солон-Пресс, 2003. — 320 с.