Каждой организации, деятельность которой связана с обработкой конфиденциальной информации, необходимо защищать её от утечек и несанкционированного доступа. Эта задача особенно актуальна для банковского сектора, государственных, муниципальных учреждений, коммерческих компаний.

Высокая степень безопасности передачи информации достигается за счёт использования криптографической защиты [1, 8].

Безопасное хранение данных достигается путем шифрования с использованием стандартных алгоритмов. Современные процессоры позволяют программно реализовать криптографический алгоритм любой сложности, однако специализированный аппаратный блок, разработанный для реализации конкретного алгоритма, будет осуществлять преобразование данных в несколько раз быстрее [2–4]. Следовательно, применение контроллера, оснащенного сопроцессорами, аппаратно реализующими выполнение криптографических алгоритмов в соответствии с мировыми стандартами, открывает широкие перспективы. Тем не менее, даже для такого микроконтроллера необходимо разработать и отладить программное обеспечение, позволяющее рационально использовать его ресурсы.

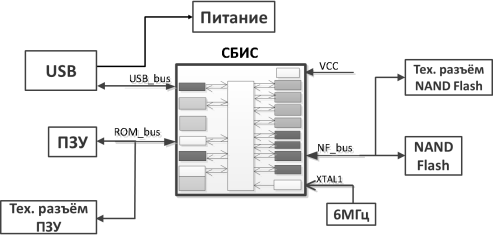

Рис. 1. Структурная схема СБИС

Эти цели достигаются с помощью аппаратно-программного комплекса тестирования сложнофункциональной сбис для носителей информации со встроенными блоками криптографической защиты. Микросхема, объединяющая контроллер семейства kmx32 и периферийные устройства, предназначена для применения в составе электронных модулей различного назначения, главным образом в малогабаритных устройствах и в мобильных системах, реализующих функции шифрования и дешифрования данных, формирования и проверки электронной цифровой подписи, а также сбора и хранения данных большого объема с защитой от несанкционированного доступа.

Структура СБИС приведена на рисунке 1, а краткое описание блоков и их назначения представлены в таблице 1.

Таблица 1

Перечень внутренних блоков СБИС

|

Название блока |

Функции ихарактеристики |

|

CPU |

32-разрядный центральный процессор КМ32 |

|

ROM_Com 128KB |

128 КБ ПЗУ команд с организацией 64К16 бит |

|

RAMD 16KB |

Однопортовое ОЗУ 16 КБ с организацией 4К32 бит |

|

FMCU |

Блок управления энергонезависимой памятью данных |

|

Flash 4KB |

Блок 4 КБ энергонезависимой памяти данных |

|

CUSB |

Контроллер интерфейса USB 2.0 Host/Device, Low Speed, Full Speed |

|

CSD-card |

Контроллер интерфейса SD-card |

|

CSPI |

Контроллер интерфейса SPI |

|

DES |

Блок аппаратной поддержки алгоритма DES |

|

AES |

Блок аппаратной поддержки алгоритма AES |

|

SHA |

Блок реализует алгоритмы: хеширования по ГОСТ Р 34.11–94; вычисления/проверки электронной цифровой подписи по ГОСТ Р 34.10–2001; аппаратной поддержки алгоритма SHA-1 |

|

RSA |

Блок аппаратной поддержки алгоритма RSA |

|

CFLASH |

Контроллер энергонезависимой памяти FLASH до 16 ГБ |

|

DC-DC |

Преобразователь уровня напряжения питания VCC в уровень напряжения питания ядра VCC_Core |

|

G |

Генератор тактовой частоты процессора |

На этапе разработки структурной схемы (рис. 2) с целью уменьшения габаритных размеров устройства было принято решение задействовать минимально необходимое количество внешних выводов микросхемы. Питание платы осуществляется через интерфейс USB посредством стабилизатора напряжения 3,3 В. Интерфейс управления внешней микросхемой физического уровня USB и интерфейс SD решено не использовать. Интерфейс SPI использован только в части линии NSS для реализации возможности управления внешним светодиодом.

Рис. 2. Структурная схема комплекса

При разработке принципиальной схемы была реализована защита цепей питания от помех низких частот путем установки электролитического конденсатора большой емкости, а также защита от помех высокой частоты путем установки керамических конденсаторов.

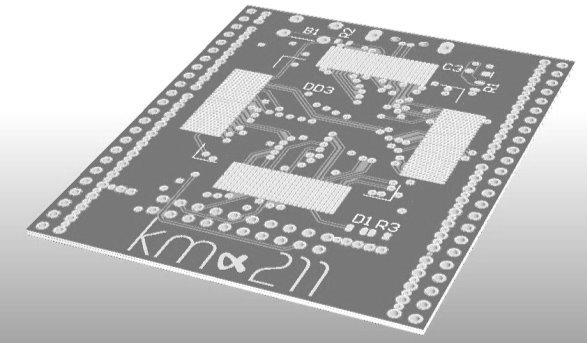

На этапе проектирования печатной платы решались задачи минимизации габаритных размеров устройства и реализации возможности наблюдения за состояниями шин интерфейсов внешних микросхем ПЗУ и FLASH, а также была реализована возможность замены внешней микросхемы ПЗУ. Печатная плата (рис. 3) состоит из четырех проводящих слоев на жестком диэлектрическом основании. Один из внутренних слоев отведен для цепей питания и заземления. Для сигнальных линий, реализующих коммутацию всех элементов платы, отведены остальные три слоя.

Плата произведена компанией «РЕЗОНИТ» и соответствует ГОСТ 23752–79, класс точности 4.

Рис. 3. Трехмерная модель печатной платы

Специализированное программное обеспечение для тестирования опытного образца СБИС представляет собой набор программ, написанных на ассемблере для процессоров семейства км32.

Пакет программ включает в себя тесты необходимого функционала процессорного ядра, памяти, и периферийных блоков. Каждая программа написана таким образом, что в случае удачного исхода или возникновения ошибки в ходе проверки процессор попадает в цикл, в котором состояние шины адреса команд не меняется. Благодаря этому программному решению процесс тестирования упрощается, так как отсутствует необходимость задействовать какие-либо интерфейсы для вывода результата проверки.

Для проведения комплекса проверочных испытаний организовано рабочее место, имеющее в составе измерительные приборы:

‒ мультиметр для проверки целостности цепей питания и информационных шин, а также для контроля корректности работы стабилизатора напряжения 3,3 В;

‒ логический анализатор для наблюдения за состоянием логических информационных сигналов;

‒ осциллограф для наблюдения за изменением напряжения в линиях в зависимости от времени (исследования наличия или отсутствия помех в цепях, наблюдения за обменом по дифференциальной линии интерфейса USB, проверки частоты, формируемой кварцевым генератором 6 МГц);

‒ ПЭВМ с программатором для разработки и компиляции тестового программного обеспечения с последующим переносом бинарного кода в микросхему ПЗУ.

Наличие всех вышеперечисленных технических средств обеспечивает возможность провести функциональное тестирование СБИС и аттестацию проверяющего устройства.

Сборка устройства происходит последовательно и представляет собой несколько этапов. При помощи мультиметра, работающего в режиме детектора нулевого сопротивления производится проверка целостности цепей питания, а также отсутствие коротких замыканий между сигнальными цепями и цепью земли. На плату устанавливаются пассивные элементы (в том числе и разъемы) и стабилизатор напряжения. Плата подключается к ПК посредством USB разъема. При помощи мультиметра, работающего в режиме вольтметра, проверяется напряжение, формируемое преобразователем. При помощи осциллографа проверяется уровень помех в цепи питания. Плата отключается от ПК, производится монтаж СБИС и внешней микросхемы NAND Flash. Производится установка адаптера ПЗУ посредством предусмотренного для этой цели разъема. После этого устройство изготовлено и готово к дальнейшей эксплуатации.

Полная проверка устройства проводится путем загрузки соответствующего ПО во внешнюю микросхему ПЗУ. К её шине адреса подключается логический анализатор, при помощи которого отслеживается правильность выполнения алгоритма программы.

Заключение

В ходе выполнения данной работы был разработан специализированный аппаратно-программный комплекс для тестирования сложнофункциональной СБИС для носителей информации со встроенными блоками криптографической защиты. По результатам проведения комплекса тестовых проверок было установлено, что ядро, внутренние периферийные блоки и блоки интерфейсов работают в полном соответствии с техническим заданием. Устройство позволяет выполнять обмен данными посредством интерфейса USB и интерфейса внешней микросхемы FLASH. Работоспособность внутренних сопроцессоров криптографических алгоритмов (AES, DES, ECDSA) позволяет выполнять преобразование данных в соответствии со стандартами криптографических алгоритмов.

Возможность легкой замены микросхемы внешней ПЗУ открывает широкий спектр возможностей для дальнейшей разработки и отладки специализированного программного обеспечения.

Литература:

- Schneier B. Data and Goliath: The Hidden Battles to Collect Your Data and Control Your World. — W. W. Norton & Company, March 2015, p. 320.

- Михайлюк Т.Е, Жернаков С. В. К вопросу об аппаратной реализации модуля потокового шифрования для комплексной системы защиты информации // Вестник УГАТУ = Vestnik UGATU. 2015. № 4 (70). URL: http://cyberleninka.ru/article/n/k-voprosu-ob-apparatnoy-realizatsii-modulya-potokovogo-shifrovaniya-dlya-kompleksnoy-sistemy-zaschity-informatsii.

- Родионов А. Ю. Архитектура криптографического сопроцессора на ПЛИС // Вопросы защиты информации. — 2016. — № 3.

- Андреев А. Е., Силкин И. М., Шафран Ю. В. Прогнозирование производительности при реализации алгоритмов на гибридных архитектурах с сопроцессорами // Современные проблемы науки и образования 2012 № 3. URL: http://www.science-education.ru/ru/article/view?id=6389)

- Federal Information Processing Standards Publication 46–3 — October 25, 1999.

- Federal Information Processing Standards Publication 197 — November 26, 2001

- Кролевецкий А. В. Производительность ГОСТ шифрования на х86 и GPU процессорах // Научно-практическая конференция «РусКрипто'2014»: 16-я Междунар. конф.: тр. конф. М.: Код Безопасности, 2014. 17 с.

- Шнайер Б. Прикладная криптография. Протоколы, алгоритмы, исходные тексты на языке Си. — М.: Триумф, 2002.