В данной работе рассматриваются платы Altera на базе ПЛИС.

Ключевые слова: программируемая логическая интегральная схема, плата, контроллер, интерфейс, светодиоды.

В настоящее время возрастает потребность в качественном производстве специализированных устройств, ускоряющих выполнения различных задач. Проектирование устройства для решения одной задачи экономически не востребовано, так как оборудования изготавливаются в нескольких экземплярах и имеют достаточно высокий диапазон цен.

Наиболее универсальным изобретением являются устройства, реализованные на микросхемах программируемой логической интегральной схеме (ПЛИС).

Реализация на ПЛИС имеет преимущество перед оборудованием, реализация которого происходит в аппаратном виде, ведь переконфигурировать данное оборудование намного легче. ПЛИС используют для решения несложных операций над крупными объемами данных.

Рассмотрим устройства, разработанные на базе ПЛИС фирмы Altera.

А именно полноценные отладочные платы.

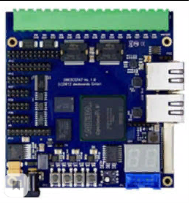

Недорогая макетная плата Mercury Code Cyclone V промышленного назначения.

Рис. 1. Макетная плата Mercury Code Cyclone V

DBC5CEFA7 — четвёртое поколение макетных плат на основе недорогой ПЛИС FPGA 5CEFA7F27C7N

Ряд периферийных устройств промышленного назначения который реализован на плате.

Состав платы имеет:

– двухканальный контроллер 10/100 Мбит/ с Ethernet

– приемопередатчик сдвоенный CAN

– приемопередатчик RS-485 четерыхканальный

– одноканальный приемопередатчик RS-232

– интерфейс LVDS низковольтный дифференциальный для подключения TFT ЖКИ

– восемь светодиодов

– четыре кнопки — клавиши навигации

Интерфейс платы оснащен 32-мя линиями ввода/ вывода общего назначения (GPIO) с уровнем сигнала 3.3 В, 16-ю линиями ввода/вывода, уровень сигнала которых может быть определен пользователем. Также 16-ю линиями с уровнем сигнала 24 В для прямого назначения с программируемыми логическими контроллерами.

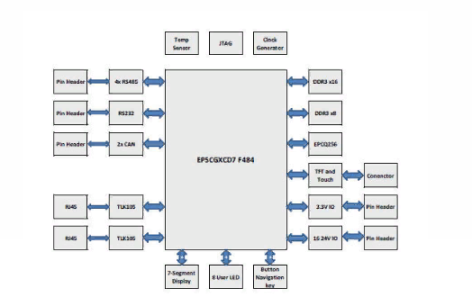

Рис. 2. Архитектура платы Mercury Code Cyclone V

Отличительные особенности:

– ПЛИС FPGA 5CEFA7F23C7N

– Конфигурационная память EPCQ256

– Аппаратный контроллер 16-битной памяти DDR3

– Программный контроллер 8-битной памяти DDR3

– Электрически стираемая перепрограммируемая память (EEPROM) Atmel CryproMemory

– Интегрированный источник питания на 1.1 В / 1.5 В / 2.5 В / 3.3 В / 5 В / 12 В

– Внешний блок питания от сети 220 В

– Размеры: 100 мм x 103 мм

Недорогое функциональное инструментальное средство обеспечивает разработку и отладку приложений на базе ПЛИС типа Система-на-Кристалле семейства Cyclone V компании Altera.

Рис. 3. Плата на основе ПЛИС FPGA сеиейства Cyclone V SoC

Плата выполнена на основе ПЛИС FPGA сеиейства Cyclone V SoC с процессорной подсистемой HPS на базе двухъядерного процессора ARM Cortex-A9, оснащенной набором периферийных модулей, контроллеры Ethernet, USB, SPI, I 2 C, UART интерфейсов, microSD карт памяти и линии ввода/вывода общего назначения.

Порты ввода/вывода подключены к разъемам, порты обеспечивают поддержку однополярных 3.3 Вт сигналов.

Отличительные особенности:

– ПЛИС FPGA семейства Cyclone V SoC: 5CSEBA6U23C7N

– Аппаратный двухъядерного процессора ARM Cortex-A9

– 110000 логических элементов

– 112 блоков DSP

– 5.4 Мбит RAM памяти

– Конфигурационная память EPCQ256

– Память DDR3 128Мх32

– Слот для карт памяти microSD

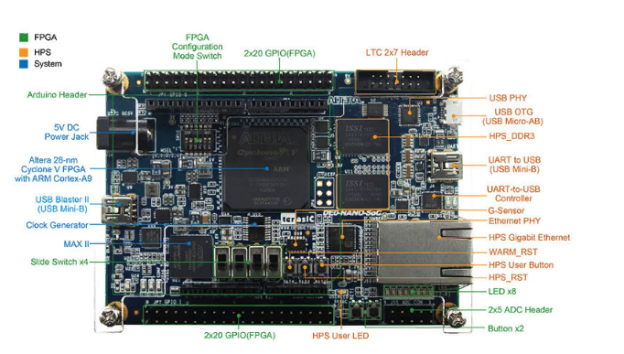

Рис. 4. Плата DE0-Nano-SoC Kit/Atlas-SoC Kit

Отличительные особенности :

– SoC: SE 5CSEMA4U23C6N

– RAM: 1GB DDR3 SDRAM

– Flash: нет

– Ethernet: 10/100/1000

– HDMI: нет

– Размер: 69x96 мм

– Arduino hesder: есть

– Цена: $99 (академическая цена $90)

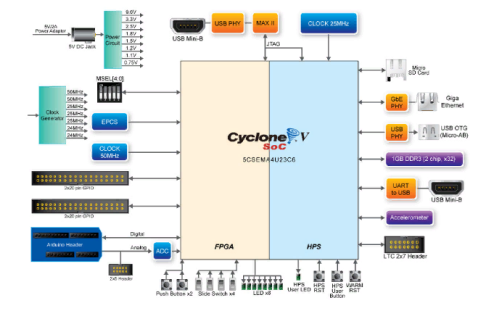

Рис. 5. структурная схема платы

Заключение

После рассмотрения нескольких вариантов плат, мы можем сделать вывод, что можно подобрать плату с отличительными особенностями. Отладочные платы имеют необходимую инфраструктуру и набор портов и интерфейсов, на базе которых можно построить полноценное изделие.

Любой разработчик может найти плату, подходящую для выполнения необходимых задач. Отладочные платы купить можно практически в любой компании, которая занимается поставкой электронных компонентов.

Литература:

- Altera: DB5CEFA7 — макетная плата Mercury Code на базе ПЛИС FPGA серии Cyclone V компании Altera. — Текст: электронный // Новое в мире полупроводников: [сайт]. — URL: http://www.ebvnews.ru/category/technical/altera/page/2 (дата обращения: 23.11.2020).

- Шишкин, Ф. Д. Особенности программируемых логических устройств / Ф. Д. Шишкин, Н. В. Горячев, В. А. Трусов. — Текст: непосредственный // Молодой ученый. — 2015. — № 1 (81). — С. 115–117. — URL: https://moluch.ru/archive/81/14747/ (дата обращения: 23.11.2020).

- Продукция корпорации Altera. — Текст: электронный // Продукция корпорации Altera: [сайт]. — URL: http://altera.ru/production.html (дата обращения: 23.11.2020).