В данной статье приводится пример разработки четырёхразрядного арифметико-логического устройства с десятеричной коррекцией. Приводятся структурные и принципиальные схемы разрабатываемого устройства.

Ключевые слова: арифметико-логическое устройство, электронные микросхемы, корректор, интегральные микросхемы, сумматор, аккумулятор, корректор, контроллер, интерфейс, двоично-десятичная система счисления.

Введение

Широкое распространение электронных вычислительных приборов, а также рост количества информации приводят к необходимости разработки новых вычислительных устройств. В данной статье приведен пример разработки арифметико-логического устройства (АЛУ), способного выполнять основные арифметические операции. Разработка АЛУ является первым шагом в разработке электронных вычислительных устройств.

Ниже будет рассмотрена разработка АЛУ, способного выполнять арифметические и логические операции с четырехбитными словами. Оно сможет выполнять побитовое логическое сложение, побитовое логическое умножение, арифметическое сложение, а также может быть использовано в качестве обычного регистра. Результат вычислений устройства будет представляться в двоично-десятиной системе счисления.

Предлагаемое АЛУ может использоваться в вычислительных интерфейсах человек — ЭВМ. Например, простейшем калькуляторе, или базовой ЭВМ.

Устройство АЛУ

Арифметико-логическое устройство — блок процессора, который под управлением устройства управления служит для выполнения арифметических и логических преобразований (начиная от элементарных) над данными, называемыми в этом случае операндами. Разрядность операндов обычно называют размером или длиной машинного слова.

По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

По способу представления чисел различают АЛУ:

− для чисел с фиксированной точкой;

− для чисел с плавающей точкой;

− для десятичных чисел.

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие приём из других устройств (например, памяти) операндов, их преобразование и выдачу результатов преобразования в другие устройства. Арифметико-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определённых микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами.

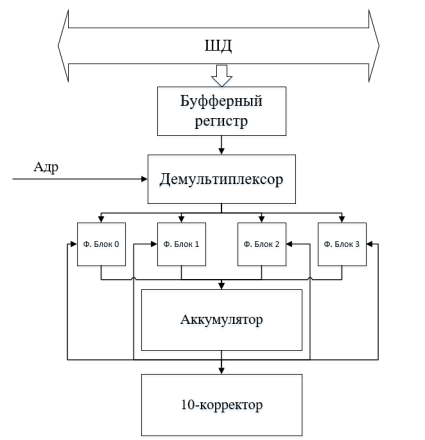

Структурная схема четырёхразрядного АЛУ

Четырехразрядное АЛУ с десятеричной коррекцией состоит из двух функциональных блоков: четырехразрядное арифметико-логическое устройство и десятеричный корректор результата. Для удобства восприятия рассмотрим разработку этих двух структурных элементов отдельно.

Для функционирования АЛУ необходимо определить шины, с которыми будет взаимодействовать разрабатываемое устройство. Из специфики устройства это:

− шина данных;

− шина команд.

Шина данных в данной работе представляет собой четырехразрядную шину. Значения в ней задают 4 ключа, соединенные с питанием. Главная задача шины данных — передача в АЛУ операндов.

Шина команд в данной работе представляет собой двухразрядную шину. Значения в ней также задаются с помощью ключей. Главная задача шины команд — передача в АЛУ управляющих сигналов, которые будут задавать функцию, которая будет работать с операндами АЛУ.

Из шины данных в буферный регистр попадает значение одного из аргументов. Это необходимо для того, чтобы шина данных могла выполнять другие задачи, пока АЛУ производит вычисления.

Из этого регистра данные попадают в демультиплексор, который имеет 4 входа (по количеству бит АЛУ) и 4 выхода, по количеству реализуемых функций АЛУ («Загрузка», «Сложение», «И», «ИЛИ»). В общем случае демультиплексор может иметь N выходов, по количеству реализуемых устройством функций.

Демультиплексор управляется уже упомянутой выше шиной команд. Шина команд имеет 2-битовую линию. Именно такое количество необходимо для демультиплексирования данных регистра в 4 линии для передачи в блоки расчета функций. В общем случае необходимо не меньше log2N бит в линии команд для реализации N функций АЛУ.

Каждый функциональный блок (часть АЛУ, выполняющая определенную функцию) имеет два четырех битных входа (разрядность операндов АЛУ). Первый вход соединен непосредственно с определенной линией демультиплексора, второй вход соединен с аккумулятором, специальным регистром, в котором хранится результат вычисления функции АЛУ.

Выходы каждого функционального блока подключаются к аккумулятору. Из аккумулятора результат вычислений попадает, как было сказано выше, попадает на второй вход функциональных блоков, а также в следующую часть устройства — десятеричный корректор.

Структурная схема разрабатываемого АЛУ представлена на рисунке 1.

Рис. 1. Структурная схема арифметико-логического устройства с десятеричной коррекцией

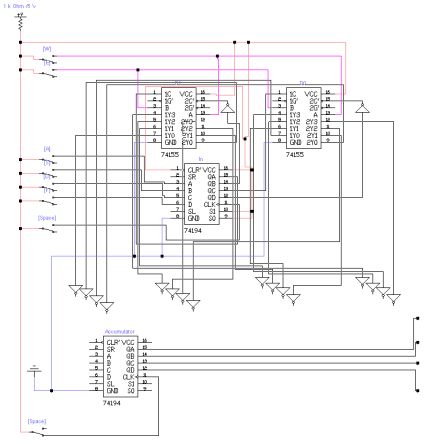

Разработка принципиальной схемы устройства

Элементная база арифметико-логического устройства с десятеричной коррекцией приведена ниже:

− микросхема 74194 (сдвиговый регистр);

− микросхема 74155 (распределитель данных);

− микросхема 4515 (мультиплексор);

− простые сумматоры;

− логические инверторы;

− логические элементы «И»;

− логические элементы «ИЛИ».

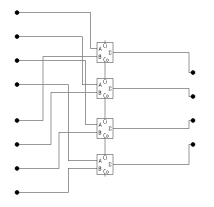

Принципиальная схема управляющего модуля АЛУ представлена на рисунке 2.

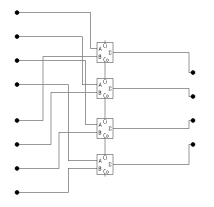

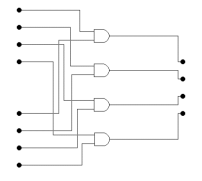

Принципиальные схемы функций АЛУ представлены на рисунках 3–5.

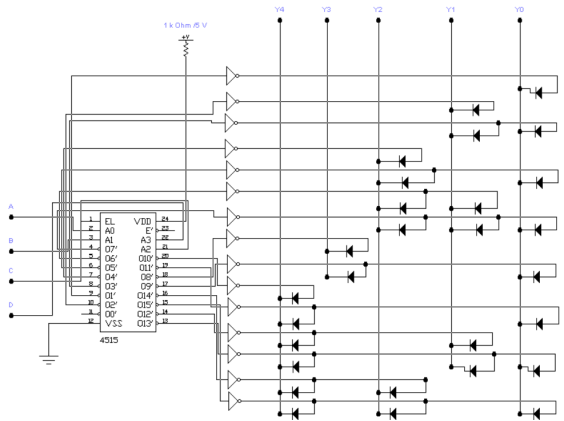

Принципиальная схема десятичного корректора представлена на рисунке 6.

Рис. 2. Принципиальная схема управляющего модуля АЛУ

Рис. 3. Принципиальная схема функции «ИЛИ» АЛУ

Рис. 4. Принципиальная схема сумматора АЛУ

Рис. 5. Принципиальная схема функции «И» АЛУ

Рис. 6. Принципиальная схема десятичного корректора

Вывод

В статье был продемонстрирован способ разработки арифметико-логического устройства с десятичной коррекцией. Устройство можно использовать в простейших вычислительных машинах, таких как калькуляторы и котроллеры.