Статья посвящена описанию процесса проектирования и разработки четырехразрядного арифметико-логического устройства с восьмеричной коррекцией.

Ключевые слова: АЛУ, архитектура, центральный процессор, логические элементы, микросхема, 4028cb, сумматор, ni multisim.

Введение

Одним из основных блоков процессора ЭВМ является АЛУ. АЛУ служит для выполнения арифметических и логических преобразований данных.

Арифметико-логическое устройство в зависимости от выполнения функций можно разделить на две части:

— микропрограммное устройство (устройство управления), задающие последовательность микрокоманд (команд);

— операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

Арифметико-логическое устройство

Арифметико-логическое устройство — блок процессора, который под управлением устройства управления служит для выполнения арифметических и логических преобразований (начиная от элементарных) над данными, называемыми в этом случае операндами. Разрядность операндов обычно называют размером или длиной машинного слова.

Концепция арифметико-логического устройства предложена в 1945 году Джоном фон Нейманом в публикации по EDVAC; она стала одной из составляющих ставшей классической фон-неймановской компьютерной архитектуры.

Восьмеричная коррекция

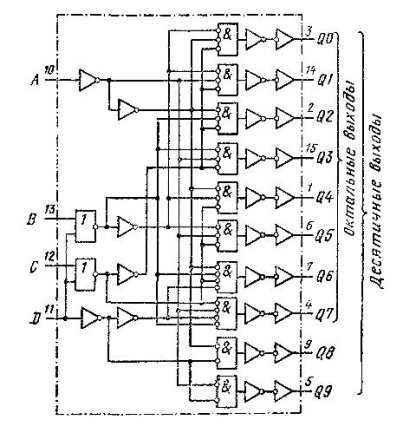

Используемая для восьмеричной коррекции микросхема 4028BD является аналогом микросхем К561ИД1 и К176ИД1. Рассмотрим работу этих микросхем.

Микросхемы К561ИД1 и К176ИД1 (CD4028A, CD4028) ― универсальный дешифратор. Дешифраторы К561ИД1, К176ИД1 (CD4028A, CD4028) применяется для преобразования входного четырехразрядного двоично-десятичного кода в десятичный или четырехразрядного двоичного в октальный.

Дешифраторы К561ИД1, К176ИД1 (CD4028A, CD4028), на рисунке 1 имеют десять выходов (при октальном, восьмеричном коде используются восемь выходов), а также четыре входа А ― D (для получения остального кода необходимы только три входа А ― С). Вход D, если на нём напряжение высокого уровня, используется как запрещающий при остальном преобразовании. Если вход D не используется, то на него следует подать ноль напряжения.

Рис. 1. К561ИД1, К176ИД1 (CD4028A, CD4028)

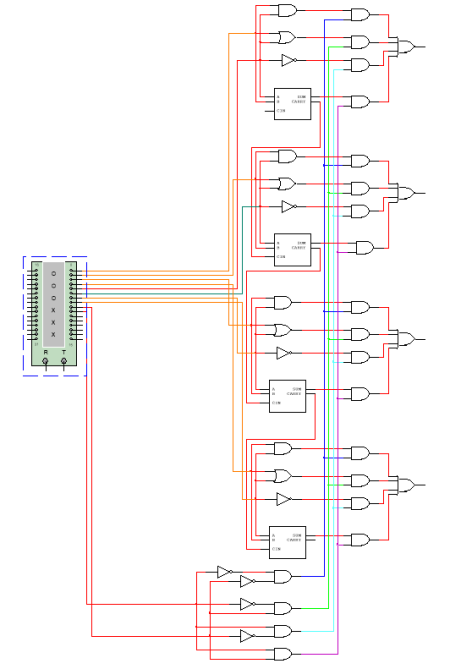

Разработка четырехразрядного АЛУ с восьмеричной коррекцией

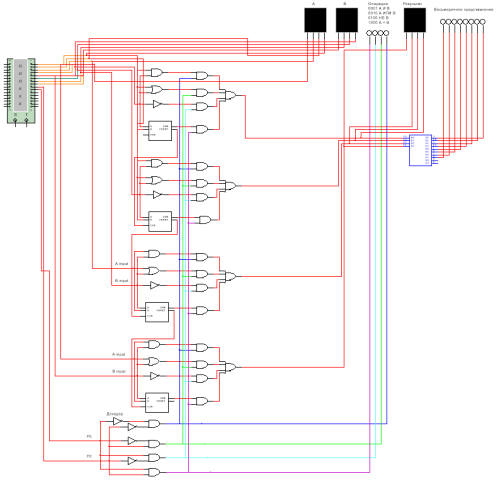

Для построения четырехразрядного АЛУ соединим четыре одноразрядных АЛУ последовательно.

Каждый выход переноса соединяем со следующим входом переноса.

В результате получим 4-разрядное АЛУ, представленное на рисунке 2.

Рис. 2. 4-х разрядное АЛУ

Восьмеричное представление

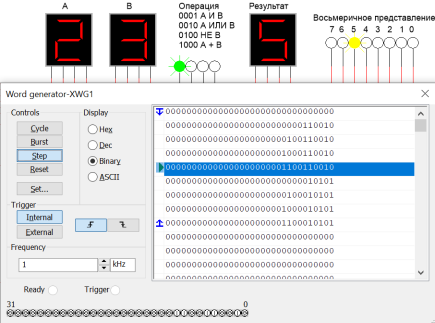

На рисунке 3 представлена готовая схема 4-разрядного АЛУ с восьмеричной коррекцией и набором цифровых индикаторов для визуального представления.

Рис. 3. 4-разрядное АЛУ с восьмеричным представлением

Результаты работы схемы

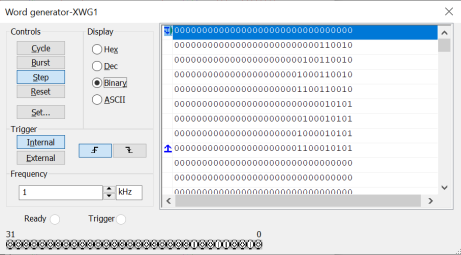

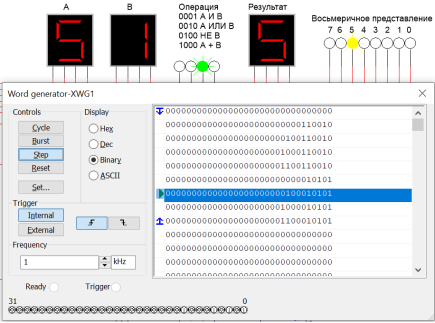

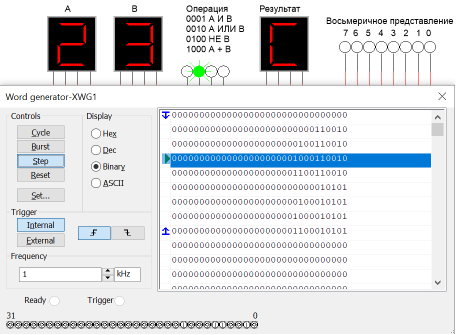

В генераторе слов необходимо установить ряд значений, отвечающих за входные данные: операцию и операнды А и В.

На рисунке 4 можно видеть, что установлено восемь цифровых слов, отвечающих за выполнение каждой операции на двух парах цифр: 2 (0010) и 3 (0011), 5 (0101) и 1 (0001).

Рис. 4. Экспериментальные данные

На рисунке 5 представлена работа схемы при отсутствии сигналов.

Рис. 5. Отсутствие сигналов

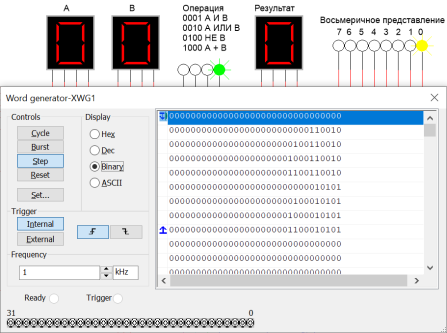

На рисунках 6 и 7 представлены результаты выполнения операций арифметического сложения, ИЛИ.

Рис. 6. А + В

Рис. 7. А ИЛИ В

Поскольку при операции инверсии может получиться цифра вне восьмеричного диапазона, то восьмеричное представление представляется как нулевое значение (рисунок 8).

Рис. 8. Результат НЕ В вне диапазона восьмеричного представления

Полный набор данных и результатов представлен в таблице 1.

Таблица 1

Результаты испытаний

|

Операнд |

Операция |

Результат |

Восьмеричное представление |

|

|

А |

В |

|||

|

0010 |

0011 |

00 |

0010 |

00000100 |

|

0010 |

0011 |

01 |

0011 |

00001000 |

|

0010 |

0011 |

10 |

1101 |

00000000 |

|

0010 |

0011 |

11 |

0101 |

00100000 |

|

0101 |

0001 |

00 |

0001 |

00000010 |

|

0101 |

0001 |

01 |

0101 |

00100000 |

|

0101 |

0001 |

10 |

1010 |

00000000 |

|

0101 |

0001 |

11 |

0110 |

01000000 |

Расчет мощности и надежности

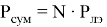

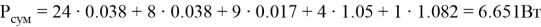

Потребляемая мощность разрабатываемого устройства будет равна сумме мощностей, потребляемых его элементами. Значения потребляемой мощности на основе справочных данных для каждого элемента определяем по формуле

В 4-разрядном АЛУ 46 элементов, указанных в таблице 2.

Таблица 2

Количество используемых элементов

|

Элемент |

Мощность |

Количество элементов |

|

И |

0.038 |

24 |

|

ИЛИ |

0.038 |

8 |

|

НЕ |

0.017 |

9 |

|

Сумматор |

1.05 |

4 |

|

4028СВ |

1.082 |

1 |

Надежность ― свойство объекта или технического устройства выполнять заданные функции, сохраняя во времени значения установленных эксплуатационных показателей.

Расчет надежности интегральной микросхемы заключается в определении среднего времени наработки до отказа.

Среднее время наработки до отказа считаем по формуле:

В таблице 3 указаны средние значения отказа.

Таблица 3

Интенсивность отказа

|

Элемент |

Время отказа,

|

Количество элементов |

|

И |

0.023 |

24 |

|

ИЛИ |

0.023 |

8 |

|

НЕ |

0.023 |

9 |

|

Сумматор |

0.023 |

4 |

|

4028СВ |

0.021 |

1 |

Рассчитываем среднее время наработки схемы до отказа

Получаем 946969 часов. Из произведенных расчетов можно сделать вывод о высокой надежности.

Заключение

В результате работы спроектирован и разработан четырехразрядное арифметико-логического устройство с восьмеричной коррекцией. Мощность устройства равна 6.651 Вт, среднее время наработки 946969 часов.

Литература:

- ЭВМ и периферийные устройства: Учебное пособие / А. Н. Сычев — 2017. 131 с.

- Математические и логические основы электронно-вычислительной техники / О. В. Подгорнова. — М.: Академия, 2013.

- Архитектура компьютера. 6-ое изд. / Таненбаум Э., Остин Т. — СПб.: Питер, 2013. — 816 с.

- Микросхемы К561ИД1 К176ИД1(CD4028A, CD4028) [Электронный ресурс] ― https://www.microshemca.ru/M.K561ID1/