В статье предлагаются методы и средства гарантированного обеспечения синхронной передачи данных между вычислительными блоками, реализованными на ПЛИС. Рассмотрены наиболее вероятные аварийные ситуации для подсистемы передачи данных и предложены способы их парирования и минимизации влияния ошибок на формирование результата. Подсистема передачи данных, построенная на описанных принципах, была протестирована на реальном устройстве цифровой обработки сигналов. Предложенные технические решения гарантируют синхронную передачу данных, а также позволяют парировать наиболее вероятные аварийные ситуации.

Ключевые слова: программируемая логическая интегральная схема, синхронная обработка данных, транспортировка данных.

Цифровая обработка сигналов (ЦОС) — одно из наиболее динамично развиваемых и перспективных направлений современной радиотехники. Применение ЦОС в радиолокационных комплексах и комплексах связи с фазированными антенными решетками (ФАР) позволяет получить множество новых, недостижимых прежде, возможностей, таких как одновременное формирование множества независимо управляемых диаграмм направленности, адаптивное формирование диаграмм направленности, позволяющее подавлять активные и пассивные помехи, сохранение работоспособности при частичной деградации систем и т. п.

Вычислительные блоки систем ЦОС могут быть реализованы на различной элементной базе: на универсальных и специальных процессорах, специализированных интегральных схемах (ASIC) или программируемых логических интегральных схемах (ПЛИС).

Для вычислителей на основе универсальных процессоров очень трудно обеспечить синхронное поступление больших потоков данных. К тому же процессоры не имеют достаточно развитой периферии, чтобы обеспечить множество быстрых каналов передачи данных.

Применение ASIC оправдано для устройств, выпускаемых серийно. Однако при изменении алгоритмов ЦОС, требуется замена всех микросхем, что влечет существенное удорожание продукции.

В ряде работ [1, 2] описано применение реконфигурируемых вычислительных систем на основе ПЛИС в составе устройств, ориентированных на многоканальную высокопроизводительную обработку сигналов. Наличие в ПЛИС большого числа ресурсов для построения различных алгоритмов цифровой обработки сигналов и множества внешних интерфейсов дает возможность организовать в реконфигурируемых системах многопоточную обработку огромного количества данных. Кроме того, ПЛИС предполагают возможность изменения и корректировки алгоритмов работы, что обеспечивает гибкость устройств, построенных на их основе.

Комплексы цифровой обработки сигналов от фазированных антенных решеток, содержащих сотни и тысячи антенных элементов, как правило, состоят из множества вычислительных блоков, в которых необходимо производить синхронную обработку данных. Одним из простых способов осуществления синхронной обработки является синхронная передача данных, для обеспечения которой необходимо генерировать множество одновременных событий по всем узлам устройства обработки данных, например, запуск оцифровки входной информации, запуск и синхронизацию вычислительных процессов в различных блоках, и корректную передачу данных между ними. Для этого, как правило, используют генератор опорных сигналов, вырабатывающий сигнал опорной тактовой частоты и сигнал единого машинного времени [3].

В качестве линий связи для межблочного взаимодействия зачастую используются оптические каналы, обладающие широкой пропускной способностью, высокой помехоустойчивостью от внешних воздействий и низким уровнем шума. При использовании оптических кабелей разной длины неизбежно возникает рассогласование потоков данных между каналами. Использование оптических кабелей одинаковой длины также не гарантирует отсутствие задержек, потому что каналы передачи данных — это не только оптические линии, но и преобразователи электрических сигналов в оптические и обратно, а также интерфейсные модули, обеспечивающие физические и логические уровни интерфейса, и все они неизбежно вносят дополнительные задержки. Например, при проведении тренировки каналов, интерфейсный модуль каждого канала, независимо от других, вставляет такты синхронизации. Рассогласование потоков данных между оптическими каналами является недопустимым, поскольку ведет к неправильному их использованию и, как следствие, к неправильному результату обработки.

Для того чтобы гарантировать синхронный прием данных от различных каналов передачи в логические модули цифровой обработки сигналов, следует принять меры для выравнивания задержек между каналами. В данной работе предлагаются методы и средства гарантированного обеспечения синхронной передачи данных между вычислительными блоками, реализованными на ПЛИС, а также средства обработки возможных аварийных ситуаций, возникающих в каналах передачи данных между ними.

Реализация подсистемы транспортировки данных на ресурсах ПЛИС

Обработка информации в вычислительных блоках происходит непрерывно. В них генерируются длинные потоки данных, которые проблематично синхронизовать во времени относительно друг друга при их передаче между вычислительными узлами. Поэтому первым шагом для реализации алгоритма выравнивания задержек будет переход на передачу данных пакетами. Операнды при этом группируются в неразрывные фрагменты (пакеты). Для того чтобы иметь возможность вести передачу пакетов, необходимо увеличить частоту передачи данных между вычислительными узлами относительно частоты обработки данных. Получившиеся межпакетные интервалы будут использованы для осуществления выравнивания задержек пакетов в каналах.

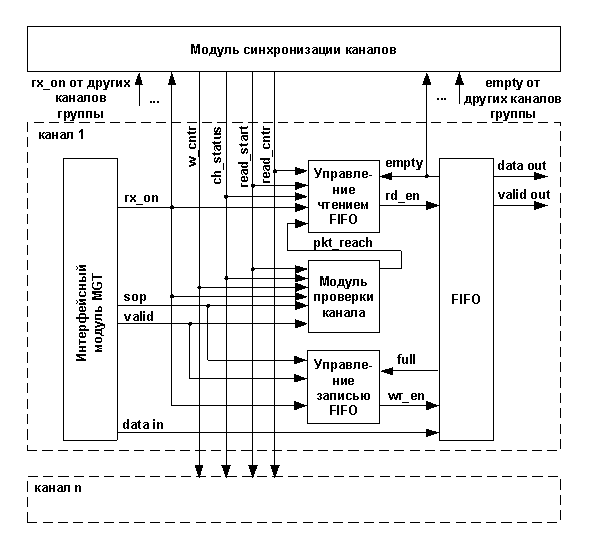

На рис. 1 представлена структура модуля, реализующего логический уровень интерфейса для группы оптических каналов.

Выравнивание задержек приема пакетов предлагается осуществлять с помощью памяти FIFO. Для каждого канала используется отдельная память FIFO и модули, управляющие логикой ее работы. Запись пакетов операндов в память FIFO происходит независимо по каждому каналу, а команда на чтение подается одновременно для всех каналов, обеспечивая выравнивание задержек приема пакетов между каналами.

Одновременно с синхронизацией осуществляется анализ аварийных ситуаций, которые необходимо обнаружить и парировать. Аварийные ситуации для подсистемы передачи данных связаны, как правило, с выходом из строя источника данных (оптических линий), при этом можно выделить два наиболее вероятных типа аварийных ситуаций:

1) полное отсутствие данных в канале в результате потери оптического соединения или по другим причинам;

2) рассогласование времени прихода пакетов в различных каналах.

Для обработки первого типа аварийных ситуаций, связанных с отсутствием данных в результате потери оптического соединения, предлагается алгоритм проверки состояния канала, который получает статус соединения от интерфейсного модуля мультигигабитного трансивера (MGT) в ПЛИС. При отсутствии соединения данные в выходном интерфейсе канала подменяются пакетами с нулевой информацией. Это необходимо для минимизации влияния отказавшего канала на результаты обработки.

Алгоритм проверки состояния канала реализуется в интерфейсном модуле MGT и представляет собой механизм контроля целостности данных, с использованием контрольного бита. При установлении оптического соединения происходит тренировка канала, по завершении которой интерфейсный модуль приемника устанавливает сигнал rx_on в единицу. На стороне передатчика контрольный бит устанавливается инверсным к первому биту данных, а на стороне приемника осуществляется их проверка. Если первый бит данных и контрольный бит одинаковые, то это говорит о нарушении целостности информации в канале, и сигнал rx_on сбрасывается в ноль, тем самым отключая канал. После отключения интерфейсный модуль продолжает проверять канал. Если в течение заданного промежутка времени фиксируется безошибочный прием данных, то сигнал rx_on устанавливается в единицу, и канал восстанавливается. Восстановленный канал проходит проверку на допустимые задержки в модуле проверки каналов и в случае успеха его данные отправляются синхронно с данным в остальных каналах.

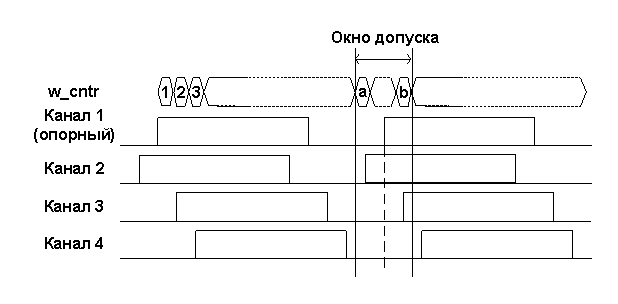

Аварийная ситуация второго типа, связанная с рассогласованием во времени прихода пакетов в различных каналах, может произойти в результате нарушений синхронизации передатчика с источниками машинного времени или опорной тактовой частоты. Для обработки данной аварийной ситуации предварительно выбирается один из каналов в качестве опорного. Затем относительно него определяется допустимая величина рассогласования времени прихода пакетов от остальных каналов (окно допуска). Если начало пакета данных поступает вне окна допуска, то данные в пакетах канала подменяются нулями.

Пример определения недопустимых задержек представлен на рис. 2.

Рис. 2. Определение недопустимых задержек

Здесь первый канал выбран в качестве опорного, на границе интервала следования пакетов опорного канала сформировано окно допуска, попадание в которое проверяется по всем остальным каналам. Начала пакетов канала 2 и канала 3 попадают в окно допуска рассогласований, поэтому они будут выравнены и приведены к началу пакета опорного канала, и отправлены дальше по системе. Начало пакета канала 4 не попадает в окно, поэтому дальше в систему обработки следует сформировать и отправить пакет, синхронный опорному с нулевой информацией.

Рассмотрим подробнее модули, управляющие логикой работы памяти FIFO.

Модуль управления записью FIFO вырабатывает сигнал записи в FIFO (wr_en) пакета данных по признаку начала пакета (sop=1) и наличию строба пакета (valid=1). Запись в FIFO осуществляется, пока есть строб пакета (valid=1). После окончания записи пакета модуль ожидает следующий пакет.

Модуль синхронизации каналов обслуживает группу каналов. Модуль определяет доступность каналов по сигналам rx_on, которые получены от интерфейсного модуля MGT. Далее модуль ожидает приема пакета в любом из доступных каналов путем контроля сигналов empty от памяти FIFO всех каналов группы. Если сигнал empty = 0, это значит, что в FIFO началась запись валидных данных. Затем относительно пакетов в первом пришедшем канале запускается счетчик окна допуска рассогласований w_cntr. Подается команда на одновременное чтение из всех FIFO (read_start) активных каналов, и запускается счетчик вычитанных данных read_counter. Одновременным чтением всех FIFO доступных каналов обеспечивается выравнивание задержек приема пакетов. Счетчики w_cntr и read_counter будут использоваться другими модулями в алгоритмах обработки второй аварийной ситуации.

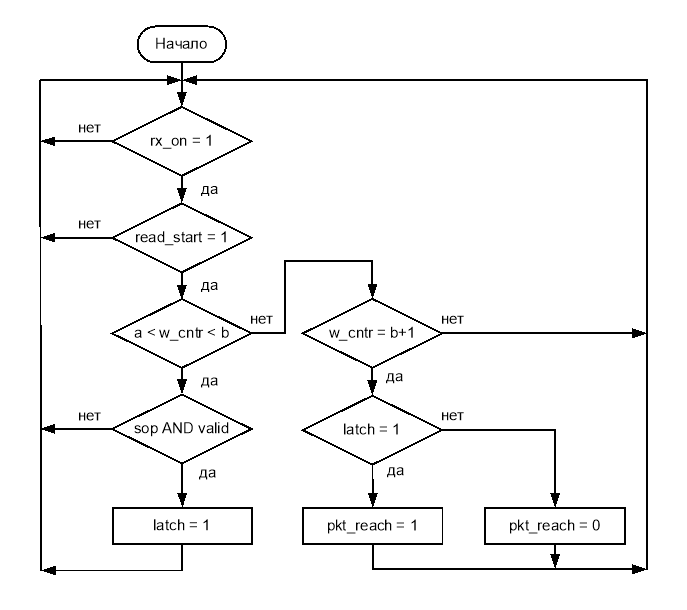

Модуль проверки канала передачи данных предназначен для отслеживания состояния канала (rx_on) и проверки попадания начала пакета (sop=1) в окно допуска, сформированного счетчиком w_cntr в модуле синхронизации каналов. При попадании начала пакета (sop=1) в окно допуска устанавливается признак pkt_reach=1 (задержка пакета в рамках допуска), который будет использован в алгоритме модуля управления чтением FIFO.

Алгоритм работы модуля проверки представлен на рис. 3.

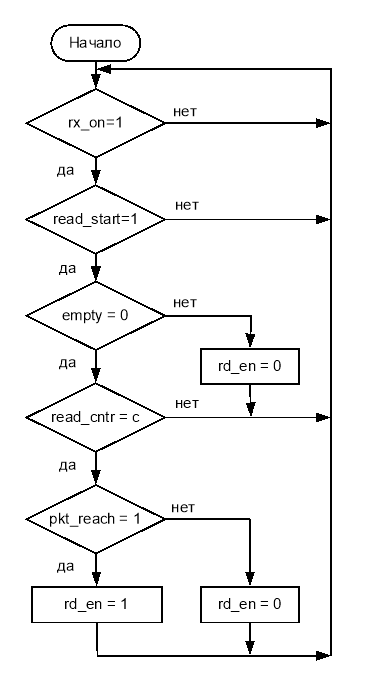

Модуль управления чтением FIFO вырабатывает сигналы чтения FIFO для формирования непрерывного потока данных, используемых для дальнейшей обработки алгоритмами ЦОС. Чтение из FIFO происходит только при попадании начала пакета (sop=1) в окно допуска (pkt_reach=1). В случае промаха (pkt_reach=0) или полного отсутствия канала (rx_on=0) на выходе FIFO (data_out) формируются пакеты с нулевыми данными.

Алгоритм работы модуля управления чтением FIFO представлен на рис. 4.

Рис. 4. Алгоритм работы модуля управления чтением FIFO

Предложенная реализация логического уровня интерфейса подсистемы передачи данных позволяет не только гарантировать синхронную передачу данных и обработку аварийных ситуаций, но и обеспечить возможность «горячего подключения» оптических линий. «Горячее подключение» полезно для систем цифровой обработки сигналов от фазированных антенных решеток, работающих в непрерывном режиме, в которых при выходе из строя какого-либо блока необходимо минимизировать время замены неисправного блока и восстановления полной работоспособности системы. В подобных подсистемах передачи данных при восстановлении оптических соединений и после замены неисправного блока могут требоваться проведение принудительной тренировки линий связи и перезапуск логических модулей подсистемы передачи данных в ПЛИС вплоть до полного сброса и пересинхронизации всей системы. Это существенно увеличивает время восстановления системы и требует дополнительных действий. В предложенной реализации обеспечивается автономное восстановление работы каналов без принудительной процедуры тренировки и синхронизации приемо-передатчиков оптических линий.

Заключение

Подсистема передачи данных, построенная на описанных принципах,была протестирована на реальном устройстве цифровой обработки сигналов. В контрольных проверках было передано 9,3*1014 байт информации на скоростях 7,2*109 бит/с в течение 24 часов.

В процессе тестирования постоянно фиксировались рассогласования каналов из-за того, что распространение по оптическим линиям от разных каналов передачи данных асинхронно. Подсистемой парировались возникающие задержки, сбоев в работе не отмечалось.

В процессе работы устройства ЦОС были также сымитированы различные аварийные ситуации. На все воздействия подсистема передачи данных реагировала корректно, парируя все аварийные ситуации.

Были протестированы функции «горячего подключения» путем физического переподключения оптических линий. Оптические соединения восстанавливались автоматически, без каких-либо дополнительных процедур.

Таким образом, можно утверждать, что предложенные технические решения при создании подсистемы межблочной передачи данных в комплексах цифровой обработки сигналов гарантируют синхронную передачу данных, а также позволяют парировать наиболее вероятные аварийные ситуации и обеспечивать возможность быстрой замены блоков в процессе работы.

Литература:

- Каляев И. А., Левин И. И., Семерников Е. А. Высокопроизводительные реконфигурируемые вычислительные системы для цифровой обработки сигналов // Труды Российского научно-технического общества радиотехники, электроники и связи имени А. С. Попова. Серия: Цифровая обработка сигналов и ее применение. Выпуск: ХII — 1. Москва. 2010 г. С. 13–18. 6 с. ISBN 978–5-904602–07–9. УДК 621.396+654+004. ББК 32.

- Дордопуло А. И., Каляев И. А., Левин И. И., Семерников Е. А. Высокопроизводительные многопроцессорные системы с реконфигурируемой архитектурой для цифровой обработки сигналов // «Вестник Концерна ПВО «Алмаз-Антей» № 2 (6). Декабрь 2011 г. с. 88–104. 17 стр.

- Левин И. И., Семерников Е. А., Буряков Д. С. Система передачи данных на основе программируемых логических интегральных схем в устройствах цифровой обработки сигналов с фазированными антенными решетками // Вестник компьютерных и информационных технологий. 2022. Т.19, № 3. С.42–50. DOI 10.14489/vkit.2022.03.pp.042–050