В статье представлена архитектура VGA-контроллера [1], способного выводить текст на экран в разрешении 80x30 символов, где каждый символ имеет размер 8x16 пикселей, что соответствует общему разрешению экрана 640x480 пикселей. Контроллер поддерживает 16 цветов для каждого символа и фона, реализованных через 4-битную цветовую палитру, где цвета кодируются комбинацией из трёх базовых каналов (красный, зелёный и синий) и одним битом для яркости. В статье также рассмотрены алгоритмы, обеспечивающие эффективную работу контроллера при минимальном использовании памяти и аппаратных ресурсов.

Ключевые слова: FPGA, видеоконтроллер, VGA, текстовый режим.

Введение

Иногда встраиваемые системы нуждаются в устройстве графического вывода, но не имеют достаточно места и памяти для сложной логики графического ускорителя. Однако существуют более простые микросхемы, видеоконтроллеры, некоторые разновидности которых способные выводить изображение на дисплей в текстовом режиме [2]. Разберем разработку такого устройства на примере процессорной системы RISC-V, разворачиваемой на FPGA плате.

Видеоконтроллер позволяет выводить информацию на экран через интерфейс VGA. VGA-модуль способен выводить 80х30 символов (разрешение символа 8x16). Таким образом, итоговое разрешение экрана, поддерживаемого модулем будет 80*8 x 30*16 = 640x480. Видеоадаптер поддерживает управление цветовой схемой для каждого поля символа в сетке 80х30. Это значит, что каждый символ (и фон символа) может быть отрисован отдельным цветом из диапазона 16-ти цветов. Пример игры с использованием символьной графики приведен на рис. 1.

![Пример игры с использованием символьной графики [3]](https://moluch.ru/blmcbn/117544/117544.001.png)

Рис. 1. Пример игры с использованием символьной графики [3]

Видеоконтроллер имеет следующие интерфейсные сигналы, подключаемые к процессорной системе:

– clk_i — системный синхроимпульс;

– clk100m_i — синхроимпульс с частотой 100 МГц;

– rst_i — синхронный сигнал сброса по положительному фронту;

– char_map_addr_i , char_map_we_i , char_map_be_i , char_map_wdata_i , char_map_rdata_o — интерфейс записи выводимого символа;

– col_map_addr_i , col_map_we_i , col_map_be_i , col_map_wdata_i , col_map_rdata_o — интерфейс установки цветовой схемы;

– char_tiff_addr_i , char_tiff_we_i , char_tiff_be_i , char_tiff_wdata_i , char_tiff_rdata_o — интерфейс установки шрифта;

– vga_r_o , vga_g_o , vga_b_o , vga_hs_o , vga_vs_o — интерфейс VGA.

Для того, чтобы вывести символ на экран, необходимо использовать адрес этого символа на сетке 80x30 (диапазон адресов char_map ). К примеру, мы хотим вывести символ в верхнем левом углу (т. е. нулевой символ нулевой строки). Это нулевой символ в диапазоне адресов char_map . Запись по этому адресу приведет к отображению символа, соответствующего ASCII-коду, пришедшему на char_map_wdata_i .

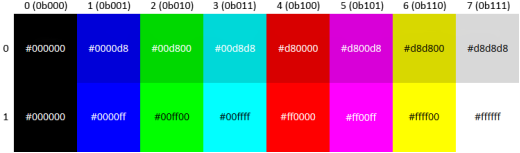

Цветовая схема каждой позиции состоит из двух цветов: цвета фона и цвета символа. Оба эти цвета выбираются из палитры 8 цветов, каждый из которых содержит два оттенка: цвет на полной яркости и цвет на уменьшенной яркости (см. рис. 2). Один из цветов — черный, оба его оттенка представляют собой один и тот же цвет. На рис. 2 приведены коды цветов и их RGB24-значения:

Рис. 2. Цветовая палитра VGA-модуля

Код цвета формируется следующим образом: старший бит определяет яркость оттенка цвета. Оставшиеся 3 бита кодируют используемый канал:

– 0 бит кодирует использование синего канала;

– 1 бит кодирует использование зеленого канала;

– 2 бит кодирует использование красного канала.

Таким образом, для установки цветовой схемы, необходимо выбрать два цвета из палитры, склеить их (в старших разрядах идет цвет символа, в младших — цвет фона) и записать получившееся 8-битное значение по адресу выбранной позиции в диапазоне адресов цветовой схемы ( color_map ).

Данный модуль поддерживает 256 сканкодов. Следовательно, для хранения шрифта под каждый из 256 сканкодов требуется 16 * 256 = 4 KiB памяти.

Для хранения цветов требуется 80 * 30 = 2400 B памяти.

Для хранения сканкодов требуется тоже 2400 B памяти.

Таким образом, видеоконтроллер использует 8896 B памяти.

Если бы контроллер использовал не текстовый, а графический режим, при том же разрешении и цветовой схеме, то потребовалось бы гораздо больше памяти: 640 * 480 = 307200 B.

Разработка модуля

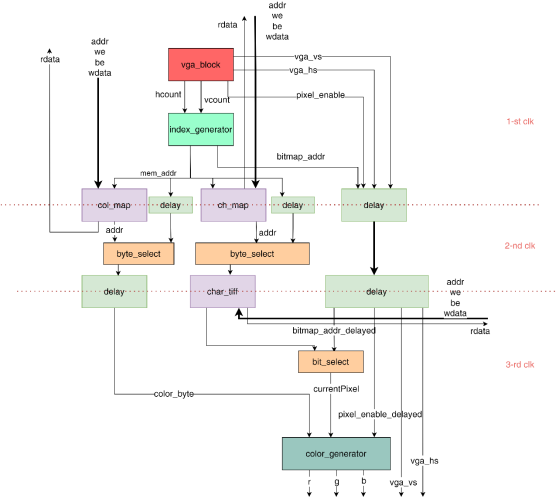

Схема видеоконтроллера представлена на рис. 3.

Рис. 3. Схема VGA-видеоконтроллера

vga_block создает импульсы вертикальной и горизонтальной синхронизации. Спецификация VGA накладывает ограничение на длительность импульсов в зависимости от разрешения и частоты обновления экрана, выраженное в герцах. Устройство отсчитывает временные интервалы, опираясь на тактовый генератор. Требуется для выбранного нами разрешения частота 25.175 МГц, обычно округляемая до 25 МГц. Погрешность 0.175 МГц с учетом разрешения допустимая. Блок содержит делитель частоты на случай, если 25 МГц не могут быть поданы из внешней среды: кратные частоты делятся до 25 МГц. Делитель реализуется на регистрах, поэтому частота, снимаемая с них, уступает в качестве системной частоте. Питать регистры vga_block напрямую с выходов регистров делителя не рекомендуется. Поэтому регистры питаются от качественной системной частоты, а частоты из делителя является сигналом разрешения обновления регистров. Кроме синхроимпульсов vsync , hsync модуль выдает vcount и hcount , указывающие на вертикальную и горизонтальную позицию, рисуемого пикселя.

index_generator преобразуют позицию пикселя из формата двумерного индекса строка-столбец в одномерный индекс. Преобразование выполняется как для позиции символа, так и для позиции пикселя в этом символе.

Формула для символа: ch_map_addr = floor( vcount / 16) * 80 + floor( hcount / 8)

Формула для пикселя: bitmap_addr = vcount * 8 + hcount

Деление выполняется эффективной операцией сдвигом вправо.

Умножение на константу 80 выполняется методом сдвиг-сложение . Суть метода в том, чтобы представить константу в виде суммы степеней двойки (80 = 2^6 + 2^4). Тогда вместо затратных умножителей используются менее затратные сумматоры.

ch_map_addr используется для извлечения цвета символа из col_map и самого символа из ch_map . col_map и ch_map — 32-битные синхронные памяти, поэтому данные из них будут доступны только на следующем такте. Нужно задержать на один такт ch_map_addr в блоке delay , представляющем собой регистры задержки, чтобы затем вычленить 8-битный символ из слова памяти в модуле byte_select .

Символ из ch_map выбирает из памяти char_tiff соответствующее ему битовое изображение. Bit_select вычленяет конкретный бит на основе задержанного на два такта bitmap_addr .

color_generator преобразует цвет из закодированного формата в значения RGB каналов. Ширина RGB каналов ограничена четырьмя битами, что объясняется физическими требованиями платы, на которой разворачивается процессорная система. Можно назвать цветовую модель, реализуемую платой, RGB12. Преобразование из закодированного формата осуществляется следующим образом:

- Происходит сопоставление цвета из палитры с цветом из RGB24. Например, цвет 0b0011 соответствует #00d8d8.

- Из каждого канала RGB24 берутся только старшие четыре бита. Данное преобразование можно отнести к разряду операций квантования.

- Склеив отобранные биты, получаем RGB12.

Памяти color_map , ch_map и char_tiff являются двухпортовыми и поддерживают чтение/запись с внешнего интерфейса. Для color_map и ch_map ширина шины данных совпадает с шириной хранимого слова, однако char_tiff хранит 128 бит. Поэтому для char_tiff адрес ждет один такт в регистре, когда произойдет синхронное чтение, и используется для извлечения тридцати двух бит из 128-битного слова.

Таким образом, видеоконтроллер имеет конвейерную архитектуру, состоящую из трех стадий.

Выводы

В данной статье был разработан VGA-контроллер, предназначенный для вывода информации на дисплей в текстовом режиме. Модуль поддерживает отображение 80x30 символов с разрешением 640x480 и управляет цветовой схемой каждого символа, предоставляя 16 возможных цветов. Контроллер реализован с учетом ограничений на аппаратные ресурсы, используя эффективные алгоритмы для расчета адресов символов и пикселей, а также оптимизированные методы умножения и деления. Были учтены особенности синхронизации VGA, в том числе необходимость делителя частоты для получения нужной частоты обновления экрана. Видеоконтроллер имеет конвейерную архитектуру, состоящую из трех стадий, что позволяет ему эффективно обрабатывать данные и управлять выводом на экран.

Результаты синтеза контроллера на FPGA приведены в таблице 1.

Таблица 1

Утилизация VGA -контроллера на FPGA xc 7 a 100 tcsg 324–1

|

Назв. |

Slice LUTs |

Slice Reg. |

Slice |

LUT as Logic |

BRAM Tile |

|

vga_reg_wrap |

222 |

245 |

91 |

222 |

6 |

|

vgachargen |

222 |

70 |

76 |

222 |

6 |

|

bitmap_delay |

0 |

14 |

8 |

0 |

0 |

|

ch_map |

8 |

0 |

4 |

8 |

1 |

|

ch_map_byte_sel_dly |

0 |

2 |

2 |

0 |

0 |

|

char_tiff |

106 |

0 |

32 |

106 |

4 |

|

col_map |

8 |

0 |

3 |

8 |

1 |

|

col_map_data_dly |

10 |

8 |

6 |

10 |

0 |

|

index_generator |

6 |

0 |

3 |

6 |

0 |

|

pixel_en_dly |

0 |

2 |

2 |

0 |

0 |

|

vga_block |

48 |

30 |

15 |

48 |

0 |

|

vga_hs_dly |

0 |

2 |

1 |

0 |

0 |

|

vga_vs_dly |

0 |

2 |

2 |

0 |

0 |

Результаты синтеза контроллера под ASIC приведены в таблице 2.

Таблица 2

Утилизация VGA -контроллера при синтезе под техпроцесс 12 nm на частоте 100 MHz

САПР : Genus(TM) Synthesis Solution 19.14-s108_1

Operating conditions: tt0p8v25c (0.8В, -25°C, typical case)

|

Тип |

Инстансы |

Площадь, µm 2 |

Площадь, % |

|

sequential |

98997 |

82749.063 |

66.3 |

|

inverter |

72376 |

6779.142 |

5.4 |

|

buffer |

2956 |

759.878 |

0.6 |

|

logic |

175791 |

34478.088 |

27.6 |

|

physical_cells |

0 |

0 |

0 |

|

total |

350120 |

124766.171 |

100.0 |

Работа выполнена при финансовой поддержке Минобрнауки в рамках государственного задания на выполнение научно-исследовательской работы по Соглашению № 075–03–2024–061/5 от 21.05.2024г. «Разработка методики прототипирования электронной компонентной базы на отечественных микроэлектронных производствах на основе сервиса MPW».

Литература:

- IBM IBM VGA XGA Technical Reference Manual / IBM. — Текст: электронный // Wayback Machine: [сайт]. — URL: https://archive.org/details/bitsavers_ibmpccardseferenceManualMay92_1756350/page/n421/mode/2up (дата обращения: 06.09.2024).

- VGA text mode. — Текст: электронный // Wikipedia: [сайт]. — URL: https://en.wikipedia.org/wiki/VGA_text_mode (дата обращения: 06.09.2024).

- Rebelstar. — Текст: электронный // Wikipedia: [сайт]. — URL: https://en.wikipedia.org/wiki/Rebelstar (дата обращения: 06.09.2024).