Введение

Современные САПР цифровых систем (ЦС) предоставляют наряду с возможностью схематического проектирования, разработку ЦС при помощи языков аппаратного проектирования (HDL). К числу достоинств разработки ЦС с использованием языков аппаратного проектирования относят [1]:

ü сокращение времени цикла разработки и производства конечного устройства;

ü гибкие возможности устранения возможных ошибок в процессе проектирования;

ü возможность применения сторонних или ранее разработанных аппаратных модулей;

ü легкость при формировании сводной документации устройства для стандартов описания по ISO9001 и специфическим внутренним стандартам документирования организации заказчика/разработчика.

Наряду с преимуществами использования вариативных методов проектирования, современные САПР ЦС позволяют, в зависимости от потребностей заказчика, реализовать ЦС на основе устройств на «жесткой логике», интегральной схеме (ИС) не способной менять собственную логическую организацию, или используя программируемые логические интегральные схемы (ПЛИС), ИС с программируемой логической организацией. ПЛИС обладают следующими преимуществами перед ИС на «жесткой логике»:

ü высокое быстродействие (до 700 МГц);

ü возможность перепрограммирования в конечном устройстве;

ü высокая степень интеграции, за счет разработки ЦС на одном кристалле;

ü возможность малосерийного производства специализированных ЦС.

Таким образом, разработка ЦС с использованием ПЛИС средствами языков аппаратного проектирования актуальна уже сегодня.

Реализация микропроцессора NBITCPU 2

Рассмотрим случай разработки вычислительного устройства (ВУ) на примере микропроцессора с симметричной регистровой архитектурой в САПР WEB ISE 10.1i [4] на отладочной плате DIGILENT NEXYS 2 с ПЛИС Spartan 3E-500 [6].

Скалярным процессором называется процессор, выполняющий за один рабочий такт одну команду. Процессором с симметричной регистровой архитектурой, называется процессор, в котором результат выполнения операции может сохраняться в любой из имеющихся регистров процессора. Что упрощает:

ü для программиста программную модель данного микропроцессора;

ü для инженера-разработчика дальнейшую модификацию ВУ с целью перехода на суперскалярную и/или многоядерную архитектуру;

ü для инженера-разработчика реализацию механизмов сопряжения микропроцессора с периферийными устройствами, микроконтроллерами, датчиками и элементами вспомогательной логики.

За основу регистрового микропроцессора был использован 64-битный микропроцессор Tiny64, автором которого является Ulrich Riedel [3], переданный на правах GPL. В исходном проекте была изменена модель организации регистров и описание верхнего уровня абстракции, с целью перехода к одной общей построечной константе в качестве опорной разрядности регистров. В результате модификации, разбиение управляющей команды на поля операций выполняется автоматически. Что привело к упрощению создания симметричного регистрового микропроцессора произвольной разрядности и соответствующего модифицированным параметрам процессора - компилятору.

Структура регистровой модели полученного микропроцессора, следующая:

ü Массив из восьми регистров общего назначения R[0..7] – размером n-бит, восьмой регистр является счетчиком команд, т.е. используется в качестве назначения команды перехода к инструкции (jmp и его условные аналоги).

ü Вспомогательные регистры для исполнения команды;

ü Массив четырех флаговых регистров: регистр переноса (regC), регистра переполнения (regV), регистр отрицательного значения (regN), регистр нуля (regN);

ü Регистр адресации памяти (adrbus) размер которого определяется размерностью регистров общего назначения.

Набор инструкций реализуемого микропроцессора NBITCPU 2 состоящий из 14 команд представлен в таб. 1.

|

Мнемоническая форма |

Машинный код |

Описание |

|

ADD |

0100AAAA |

R(n)= opa+opb обновить регистр переноса, переполнения, знака |

|

SUB |

0101AAAA |

R(n)= opa-opb обновить регистр переноса, переполнения, знака |

|

MOV |

0000AAAA |

R(n)= opb из mem, или R(n) |

|

XOR |

0011AAAA |

R(n)= if ((opa==true or opb==true) and (opa!=opb) |

|

OR |

0010AAAA |

R(n)=opa||opb |

|

AND |

0001AAAA |

R(n)=opa and opb |

|

INC |

1011AAAA |

R(n)=opa++ |

|

DEC |

1100AAAA |

R(n)=opa-- |

|

Над произвольным регистром R(n) |

||

|

ROR |

0110AAAA |

циклический сдвиг вправо на фиксированную величину |

|

RORB |

1101AAAA |

циклический сдвиг вправо на один бит |

|

LSR |

0111AAAA |

логический сдвиг вправо на фиксированную величину |

|

LSRA |

1000AAAA |

логический сдвиг вправо на один бит |

|

SWAP |

1001AAAA |

меняет местами условные нибблы (полуслово процессора) |

|

SWAPB |

1010AAAA |

меняет местами восьмую часть условного ниббла и остальную часть слова |

Таб. 1. Набор команд микропроцессора

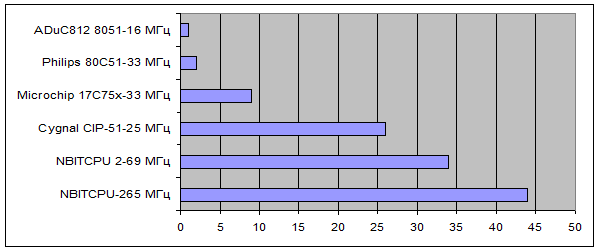

В результате компиляции кода микропроцессора и непосредственной конфигурирования ПЛИС для 64-битного регистра аккумулятора, 32 битной адресации ОЗУ – затрачено 26% вентилей ПЛИС, рабочая частота процессора составила 69 МГц. Так как, на выполнение произвольной операции затрачивается два такта, пиковая производительность разработанного ВУ NBITCPU 2 составляет 34 миллиона инструкции в секунду, 34 MIPS.

Рис. 1. Сравнение пиковой производительности микропроцессоров

NBITCPU 1, NBITCPU 2 и некоторых промышленных микропроцессоров

Сравнение производительности с ранее разработанным автором асимметричным микропроцессором NBITCPU 1 [5, c. 63-64], NBITCPU 2 описываемом в данной статье и коммерческими процессорами представлено выше на рис. 1.

Используемая при проектировании NBITCPU 2 САПР WEB ISE 10.1i [4] является бесплатной и обладает ограничением на размер проекта до 1 миллиона логических вентилей, схематический аналог трех Intel Pentium 3 микропроцессоров.

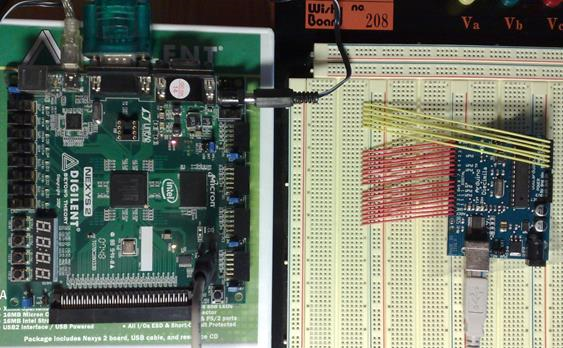

В качестве аппаратной основы процессора NBITCPU используется отладочная плата DIGILENT NEXYS 2 Spartan 3E-500 содержащая:

ü ПЛИС на 500 тыс. логических вентилей;

ü 16 Мбайт ОЗУ фирмы Micron и 16 Мбайт флэш-памяти Intel;

ü кварцевый осциллятор на 50 МГц, так же имеется возможность установки стороннего осциллятора;

ü 8 переключателей, четыре 7-ми сегментных светодиодных дисплея, 4 клавиши, USB-порт с максимальной передачей 38 Мбайт/с, PC/2 порт для подключения клавиатуры или мыши, VGA выход с разрешением 640х480 и 256 цветах, один RS232-порт с максимальная скорость приема/передачи 9600 Кбит/с;

ü разъем Hirose FX-2 для 100 МГц коммутации периферийных элементов;

ü четыре блока Pmod 2х6 контактов для подключения датчиков и устройств управления шаговыми двигателями.

Наличие развитой системы интерфейсов ввода-вывода у DIGILENT NEXYS 2 позволяет на основе процессора NBITCPU 2 реализовать ЦС специального назначения.

Рис. 2. Тестовый стенд процессора NBITCPU 2

Для реализации интерфейса сопряжения с микроконтроллерами использовалась отладочная плата Arduino Diecimila на микроконтроллере ATMEGA168 и плата контактного монтажа WISH Board 208. Тестовый стенд микропроцессора представлен выше на рис. 2.

Заключение

Таким образом, разработанный в САПР WEB ISE микропроцессор с симметричной регистровой архитектурой – NBITCPU 2, обладает сравнительно большой производительностью, при 4-кратном преимуществе в разрядности оперируемых структур по сравнению с 32-битными процессорами и затратах около 26% логических вентилей кристалла ПЛИС. Оценка производительности на отладочной плате NEXYS 2 Spartan 3E-500, подтверждает эффективность разработки ЦС при помощи современных средств аппаратного проектирования, а именно ПЛИС XILINX Spartan 3e-500 и языка аппаратного проектирования VHDL.

Литература

- Максфилд К. Проектирование на ПЛИС. Курс молодого бойца. – М.: «Додэка-XXI»,2007. – 408 с.

2. Зотов В.Ю. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР WebPack ISE. – М.: Горячая линия – Телеком, 2005. – 624 с.

- Сайт разработчиков открытых ЦС [Электронный ресурс]. - Режим доступа http:// opencores.com/, свободный.

- Официальный сайт Xilinx [Электронный ресурс]. - Режим доступа http://www.xilinx.com /webpack/index.htm, свободный.

5. Усатюк В.С. Отчет о создании микропроцессора с ассиметричной архитектурой регистров на основе ПЛИС семейства SPARTAN-3E средствами языка аппаратного проектирования VHDL. Сборник трудов VII Всероссийской научно-практической конференции студентов, аспирантов и молодых ученых «Молодежь и современные информационные технологии». Томск, 25 - 27 февраля 2009 г., ч.1. Томск: Изд-во СПБ Графикс–354 с.

6. Nexys 2 Board Reference Manual. Revision: January 21, 2008. Официальный сайт Digilent [Электронный ресурс]. - Режим доступа [http://www.digilentinc.com/], свободный.

7. Pong P. C. FPGA prototyping by VHDL examples Xilinx Spartan – 3 versions. John Wiley & Sons 2008. - 440 p.